文档编号: AN1043

上海东软载波微电子有限公司

# 应用笔记

## **HW3182 Hardware Reference Design**

V1.1 1/8

### 修订历史

| 版本   | 修订日期      | 修改概要                     |  |

|------|-----------|--------------------------|--|

| V1.0 | 2020-6-4  | 初版                       |  |

| V1.1 | 2024-4-28 | 1.1 小节增加对射频网络元器件稳定性要求的描述 |  |

地 址:中国上海市徐汇区古美路 1515 号凤凰园 12 号楼 3 楼

E-mail: support@essemi.com 电 话: +86-21-60910333 传 真: +86-21-60914991

网 址: http://www.essemi.com

#### 版权所有©

#### 上海东软载波微电子有限公司

本资料内容为上海东软载波微电子有限公司在现有数据资料基础上慎重且力求准确无误编制而成,本资料中所记载的实例以正确的使用方法和标准操作为前提,使用方在应用该等实例时请充分考虑外部诸条件,上海东软载波微电子有限公司不担保或确认该等实例在使用方的适用性、适当性或完整性,上海东软载波微电子有限公司亦不对使用方因使用本资料所有内容而可能或已经带来的风险或后果承担任何法律责任。基于使本资料的内容更加完善等原因,上海东软载波微电子有限公司保留未经预告的修改权。使用方如需获得最新的产品信息,请随时用上述联系方式与上海东软载波微电子有限公司联系。

## 目录

## 内容目录

| 第 | 1 章     | 原理图参考设计  | 4 |

|---|---------|----------|---|

|   | 1.1     | 原理图      | 4 |

|   | 1.2     | 外围电路 BOM | 6 |

|   | 1.3     | 射频电路 BOM | 6 |

| 第 | 2 章     | PCB 参考设计 |   |

| 第 | 3 章     | 制版工艺     | 8 |

|   |         |          |   |

| 图 | 目录      |          |   |

| 图 | 1-1 SCH | 参考设计     | 4 |

|   |         | 参考设计     |   |

|   |         |          |   |

|   |         |          |   |

| 表 | 目录      |          |   |

| 表 | 1-1 外围  | 电路 BOM   | 6 |

| 表 | 1-2 射频  | 电路 BOM   | 6 |

| 表 | 3-1 PCB | 制版工艺参数   | 8 |

## 第1章 原理图参考设计

#### 1.1 原理图

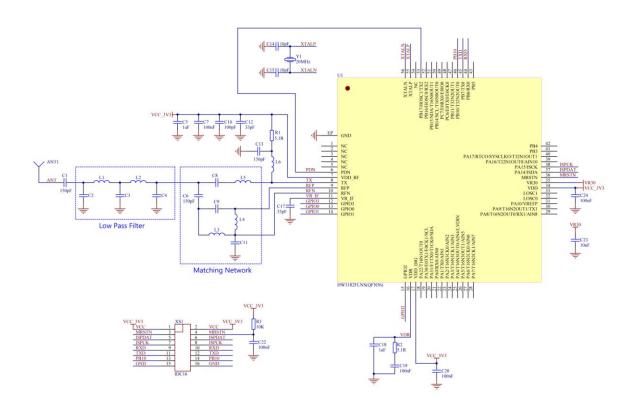

HW3182 的原理图参考设计如下图所示。

图 1-1 SCH 参考设计

电路系统主要由晶体振荡电路、TX/RX 匹配网络、低通滤波器和电源滤波电路组成。

晶体振荡电路推荐采用 20MHz 无源贴片晶体,C14、C15 是晶体负载电容,其参数将影响晶体振荡频率,请参考晶体具体规格来选择。根据应用需求的不同,推荐用户选择频率稳定度≥± 10ppm 的晶振。选取原则如下:晶体精度越高,无线设备之间载波频偏将越小,远距离通信成功率将显著提高。因此远距离应用请尽量选用高精度无源晶体。

射频网络包括阻抗匹配网络(Matching Network)和低通滤波器(Low Pass Filter)两部分。 其中低通滤波器是发射(TX)和接收(RX)共用,阻抗匹配网络则分成 TX 和 RX 两部分。对于 Direct Tie 结构,TX 和 RX 阻抗匹配网络直接通过 C6 电容连接。阻抗匹配网络实现射频收发器芯 片内部阻抗到外围 50 欧姆阻抗的变换。低通滤波器采用 LC 低通滤波电路,用于滤除有用信号以外 的高频干扰杂波。射频网络的元件选型对通信将产生很大影响,推荐选用高频器件。需要注意的是, 不同收发频率下的射频网络元件的取值是不同的(具体参考表 1-2)。此外,由于射频网络为关键电 路,使用稳定性高的元器件可提升产品质量。通常容值小于 1nF 的电容推荐采用 NPO(COG)电容, 而电感推荐采用精度较高的高频叠层电感。

低噪声的电源可显著提升射频电路的稳定性。推荐通过 LDO 稳压后给芯片供电,并且在靠近芯片电源管脚放置不同容量的电容,滤除电源上不同频率的干扰杂波,保证芯片能够稳定的工作。

HW3182 内部 RF 收发器的电源是 VDD\_RF (7 脚) 和 VDD\_DIG (17 脚), MCU 的电源是 VDD (34 脚),它们在内部是不连的,所以都需要连接到 VCC\_3V3 外部电源上。另外,虽然 MCU 电源支持 5V,然而 RF 收发器电源只支持 3.6V,而且 MCU 和 RF 的数字接口内部连接,因此,整个 SoC 芯片统一连接的外部电源电压最高为 3.6V。

若应用场景不需要进入 Power Down 模式,则 PDN 脚可以直接接地;反之,若需要进入 Power Down 模式,则 PDN 脚可接 GPIO 口来控制,参考设计选择了 PA7。

## 1.2 外围电路 BOM

下面给出外围电路 BOM。

| Part   | Designator              | Footprint  | Description        |

|--------|-------------------------|------------|--------------------|

| 10pF   | C14、C15                 | 0402       | NP0(C0G)电容,±0.25pF |

| 33pF   | C12、C17                 | 0402       | NP0(C0G)电容,±0.25pF |

| 100pF  | C10                     | 0402       | NP0(C0G)电容,±10%    |

| 150pF  | C1、C6、C13               | 0402       | NP0(C0G)电容,±10%    |

| 10nF   | C23                     | 0402       | X7R 电容,±10%        |

| 100nF  | C7、C20、C21、C22、C24      | 0402       | X7R 电容,±10%        |

| 1uF    | C5、C18                  | 0402       | X7R 电容,±10%        |

| _      | C2、C3、C4、C8、C9、C11      | 0402       | NP0(C0G)电容,±0.25pF |

|        | 02, 03, 04, 00, 09, 011 |            | (取值参考表 1-2)        |

| _      | L1、L2、L3、L4、L5、L6       | 0402       | 高频叠层电感, ±5%        |

|        | L1, L2, L3, L4, L5, L0  |            | (取值参考表 1-2)        |

| 5.1Ω   | R1、R2                   | 0402       | 电阻,±1%             |

| 10K    | R3                      | 0402       | 电阻,±5%             |

| 0Ω /NC | R4、R5                   | 0402       | 电阻,±5%,根据需要焊接      |

| 20MHz  | Y1                      | SMD3225    | 无源晶振,±10ppm        |

| HW3182 | U1                      | QFN56(7X7) | 射频 SoC 芯片          |

| 天线接口   | ANT1                    |            | 导线天线接口             |

| 邮票孔接口  | XS1                     | _          | 1.27mm 邮票孔接口       |

表 1-1 外围电路 BOM

## 1.3 射频电路 BOM

由于 HW3182 支持多个频率,,而不同频率下的射频网络元件取值略有不同。

下面给出不同频率下的射频电路 BOM。

| <b>标号</b><br>频率 | L1,L2 | C2,C4 | C3   | L5    | C8    | L3    | L4   | <b>C</b> 9 | C11   | L6    |

|-----------------|-------|-------|------|-------|-------|-------|------|------------|-------|-------|

| 315MHz          | 22nH  | 12pF  | 22pF | 33nH  | 6.8pF | 33nH  | 47nH | 4.7pF      | 10pF  | 120nH |

| 433MHz          | 18nH  | 6.8pF | 12pF | 15nH  | 6.8pF | 22nH  | 47nH | 3.3pF      | 6.8pF | 47nH  |

| 779MHz          | 5.6nH | 6.8pF | 12pF | 3.9nH | 6.8pF | 10nH  | 22nH | 3.9pF      | 3.9pF | 33nH  |

| 868MHz          | 4.7nH | 6.8pF | 12pF | 4.7nH | 6.8pF | 5.6nH | 12nH | 2.7pF      | 5.6pF | 22nH  |

| 915MHz          | 3.9nH | 6.8pF | 12pF | 3.9nH | 5.6pF | 6.8nH | 10nH | 3.9pF      | 5.6pF | 18nH  |

表 1-2 射频电路 BOM

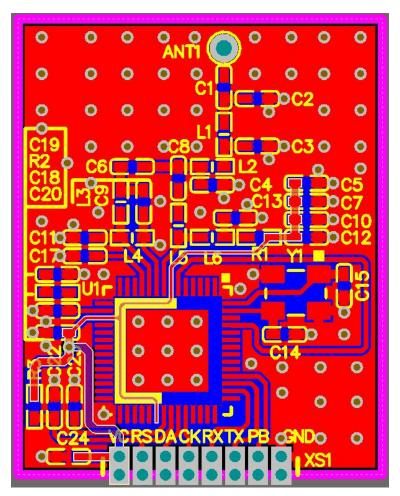

### 第2章 PCB参考设计

HW3182 的 PCB 参考设计采用双面板,注意事项如下:

- 所有元器件均布局在双面板顶层,底层需提供完整的参考地平面。

- 两个电感互连推荐采用 L 形布局,以减小互感,而其它射频元件,应尽可能紧凑排列。

- 射频走线应尽可能短; L4 连接芯片管脚 RFP、RFN 的走线是差分线,需平行、等长布线,以保证差分性能。

- 所有射频电路周围应"铺地"(即对地线铺铜),且铺地区域应均匀放置接地过孔,以降低接地阻抗。

- 数字电路和晶振电路应尽可能远离射频前端电路。

- 若电源与数字信号走底层,应避免对地平面的分割,且尽可能远离射频电路;禁止在射频 芯片下的底层区域走线,避免破坏底层地平面的完整性。推荐在芯片底部中央焊盘和周围 管脚之间的空隙区域走电源线。为了降低短路风险,可在电源走线上增加丝印进行保护。

- 滤波电容应尽可能靠近芯片电源管脚,提升滤波效果。

- 射频走线宽度和铺铜间距,可参考第3章《制版工艺》。

下面给出 PCB 参考设计图。

图 2-1 PCB 参考设计

## 第3章 制版工艺

由于高频信号的存在,在 RF PCB 制版过程中需要考虑 PCB 工厂的阻抗控制参数。下面给出的是本参考设计的制版工艺参数。

| 制版规格                     | 参数           |  |  |  |

|--------------------------|--------------|--|--|--|

| 板材                       | FR4          |  |  |  |

| 板厚 <sup>注</sup>          | 1.2mm        |  |  |  |

| 电源走线                     | 25mil        |  |  |  |

| 50 欧姆射频走线宽度 <sup>注</sup> | 20mil        |  |  |  |

| 铜厚                       | 1.4mil(1 盎司) |  |  |  |

| 接地铺铜与射频走线的间距注            | 5.1mil       |  |  |  |

表 3-1 PCB 制版工艺参数

注:为保证射频走线为50 欧姆,可以根据不同板厚,按照如下参数进行调整。以下结果为Si9000 仿真值,仅供参考。仿真假设FR4 的介电常数为4.3、绿油介电常数为4.2,这些参数对仿真结果影响较大,具体参数请与PCB厂家确认后自行仿真。如果需要更加准确的结果,则需要PCB厂家进行阻抗控制。

#### (1) 若射频走线采用 20mil 线宽:

板厚为 1.0mm 时,接地铺铜与走线间距为 5.3mil 板厚为 1.2mm 时,接地铺铜与走线间距为 5.1mil 板厚为 1.6mm 时,接地铺铜与走线间距为 5mil

#### (3) 若射频走线采用 25mil 线宽:

板厚为 1.0mm 时,接地铺铜与走线间距为 6.3mil 板厚为 1.2mm 时,接地铺铜与走线间距为 6mil 板厚为 1.6mm 时,接地铺铜与走线间距为 5.7mil

#### (3) 若射频走线采用 30mil 线宽:

板厚为 1.0mm 时,接地铺铜与走线间距为 7.6mil 板厚为 1.2mm 时,接地铺铜与走线间距为 7.1mil 板厚为 1.6mm 时,接地铺铜与走线间距为 6.6mil