# 8位MCU HR7P159BE2SA

# 数据手册

- □产品简介

- ☑ 数据手册

- □产品规格

上海东软载波微电子有限公司

2021年09月23日

## 东软载波 MCU 芯片使用注意事项

#### 关于芯片的上/下电

东软载波 MCU 芯片具有独立电源管脚。当 MCU 芯片应用在多电源供电系统时,应先对 MCU 芯片上电,再对系统 其它部件上电;反之,下电时,先对系统其它部件下电,再对 MCU 芯片下电。若操作顺序相反则可能导致芯片内 部元件过压或过流,从而导致芯片故障或元件退化。具体可参照芯片的数据手册说明。

#### 关于芯片的复位

东软载波 MCU 芯片具有内部上电复位。对于不同的快速上/下电或慢速上/下电系统,内部上电复位电路可能失效,建议用户使用外部复位、下电复位、看门狗复位等,确保复位电路正常工作。在系统设计时,若使用外部复位电路,建议采用三极管复位电路、RC 复位电路。若不使用外部复位电路,建议采用复位管脚接电阻到电源,或采取必要的电源抖动处理电路或其它保护电路。具体可参照芯片的数据手册说明。

#### 关于芯片的时钟

东软载波 MCU 芯片具有内部和外部时钟源。内部时钟源会随着温度、电压变化而偏移,可能会影响时钟源精度; 外部时钟源采用陶瓷、晶体振荡器电路时,建议使能起振延时;使用 RC 振荡电路时,需考虑电容、电阻匹配;采 用外部有源晶振或时钟输入时,需考虑输入高/低电平电压。具体可参照芯片的数据手册说明。

#### 关于芯片的初始化

东软载波 MCU 芯片具有各种内部和外部复位。对于不同的应用系统,有必要对芯片寄存器、内存、功能模块等进行初始化,尤其是 I/O 管脚复用功能进行初始化,避免由于芯片上电以后,I/O 管脚状态的不确定情况发生。

#### 关于芯片的管脚

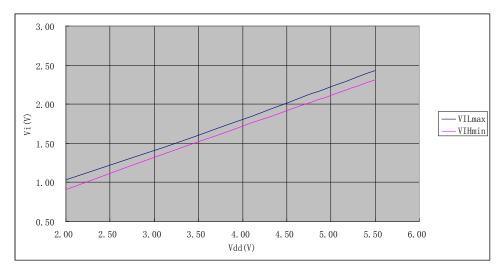

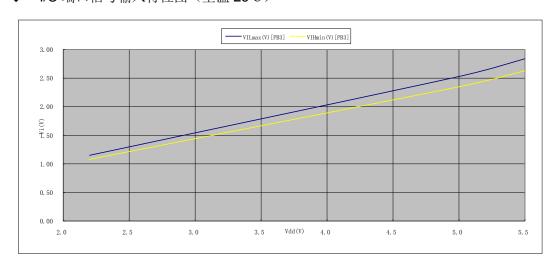

东软载波 MCU 芯片具有宽范围的输入管脚电平,建议用户输入高电平应在 V<sub>IHMIN</sub> 之上,低电平应在 V<sub>ILMAX</sub> 之下。避免输入电压介于 V<sub>IHMIN</sub> 和 V<sub>ILMAX</sub> 之间,以免波动噪声进入芯片。对于未使用的输入/输出管脚,建议设置为输入状态,并通过电阻接至电源或地,或设置为输出状态,输出固定电平。对未使用的管脚处理因应用系统而异,具体遵循应用系统的相关规定和说明。

#### 关于芯片的 ESD 防护措施

东软载波 MCU 芯片具有满足工业级 ESD 标准保护电路。建议用户根据芯片存储/应用的环境采取适当静电防护措施。应注意应用环境的湿度;建议避免使用容易产生静电的绝缘体;存放和运输应在抗静电容器、抗静电屏蔽袋或导电材料容器中;包括工作台在内的所有测试和测量工具必须保证接地;操作者应该佩戴静电消除手腕环手套,不能用手直接接触芯片等。

#### 关于芯片的 EFT 防护措施

东软载波 MCU 芯片具有满足工业级 EFT 标准的保护电路。当 MCU 芯片应用在 PCB 系统时,需要遵守 PCB 相关设计要求,包括电源、地走线(包括数字/模拟电源分离,单/多点接地等等)、复位管脚保护电路、电源和地之间的去耦电容、高低频电路单独分别处理以及单/多层板选择等。

## 关于芯片的开发环境

东软载波 MCU 芯片具有完整的软/硬件开发环境,并受知识产权保护。选择上海东软载波微电子有限公司或其指定的第三方公司的汇编器、编译器、编程器、硬件仿真器开发环境,必须遵循与芯片相关的规定和说明。

注:在产品开发时,如遇到不清楚的地方,请通过销售或其它方式与上海东软载波微电子有限公司联系。

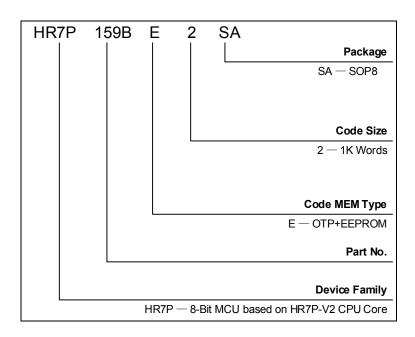

## 产品订购信息

| 型 号            | ОТР      | RAM   | EEPROM | I/O      | Timer     | PWM | LVD | 封装类型 |

|----------------|----------|-------|--------|----------|-----------|-----|-----|------|

| HR7P159BE2SA   | 1K Words | 128   | 256    | 5+1INPUT | 8-bit X 3 | 2   | 2   | SOP8 |

| TIK/F 159BE25A | TK Wolus | Bytes | Bytes  |          | ס-טונ א ט |     |     |      |

地 址:中国上海市徐汇区古美路 1515 号凤凰园 12 号楼 3 楼

E-mail: support@essemi.com 电 话: +86-21-60910333 传 真: +86-21-60914991

网 址: <a href="http://www.essemi.com">http://www.essemi.com</a>

## 版权所有©

#### 上海东软载波微电子有限公司

本资料内容为上海东软载波微电子有限公司在现有数据资料基础上慎重且力求准确无误编制而成,本资料中所记载的实例以正确的使用方法和标准操作为前提,使用方在应用该等实例时请充分考虑外部诸条件,上海东软载波微电子有限公司不担保或确认该等实例在使用方的适用性、适当性或完整性,上海东软载波微电子有限公司亦不对使用方因使用本资料所有内容而可能或已经带来的风险或后果承担任何法律责任。基于使本资料的内容更加完善等原因,上海东软载波微电子有限公司保留未经预告的修改权。使用方如需获得最新的产品信息,请随时用上述联系方式与上海东软载波微电子有限公司联系。

# 修订历史

| 版本   | 修改日期      | 更改概要                                                                                                                 |

|------|-----------|----------------------------------------------------------------------------------------------------------------------|

| V1.0 | 2017-11-8 | 初版发布。                                                                                                                |

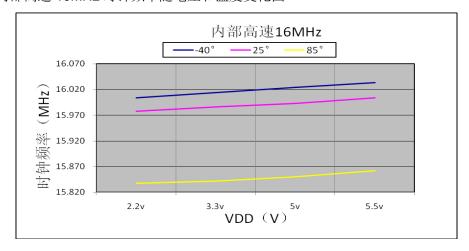

| V1.1 | 2018-9-13 | <ol> <li>更新了内部 HRC 16MHz 全温度范围的偏差为±3%,<br/>更新了 16MHz 随电压-温度变化的曲线图。</li> <li>增加下电复位电压点选择为 2.7V 或 3.4V 的建议。</li> </ol> |

| V1.2 | 2019-3-4  | <ol> <li>添加芯片上电和下电工作条件表;</li> <li>增加使能位 GIE 的补充说明;</li> <li>增加了封装尺寸的补充说明;</li> <li>变更 Logo。</li> </ol>               |

| V1.3 | 2019-7-11 | 1. 更新 LVD 章节寄存器名称;<br>2. 更新特殊功能寄存器总表中 LVD0 中断使能位和标志<br>位名称。                                                          |

| V1.4 | 2021-9-23 | 1. 更新封装尺寸参数;<br>2. 更新公司地址。                                                                                           |

## 目 录

## 内容目录

| 第1  | 二章  | Ĺ   |    |    | 芯片简介       |                     | 11 |

|-----|-----|-----|----|----|------------|---------------------|----|

|     | 1.  | . 1 |    |    | 概述         |                     | 11 |

|     | 1.  | . 2 |    |    | 应用领域       |                     | 12 |

|     | 1.  | . 3 |    |    | 结构框图       |                     | 13 |

|     | 1.  | . 4 |    |    | 管脚分配       | 图                   | 13 |

|     |     |     | 1. | 4. | . 1 8-pin  |                     | 13 |

|     |     |     | 1. | 4. | . 2        | 管脚复用说明              | 14 |

|     |     |     | 1. | 4. | . 3        | 管脚参数对照表             | 15 |

|     |     |     | 1. | 4. | . 4        | MCU 与 EEPROM 内部连线关系 | 15 |

| 第2  | 2 章 | Î   |    |    | 内核特性       |                     | 16 |

|     | 2   | . 1 |    |    | CPU 内核     | 概述                  | 16 |

|     | 2   | . 2 |    |    | 系统时钟       | 和机器周期               | 16 |

|     | 2   | . 3 |    |    | 指令集概       | 述                   | 16 |

|     | 2   | . 4 |    |    | 特殊功能       | 寄存器                 | 16 |

| 第3  | 3 章 | Î   |    |    | 存储资源       |                     | 18 |

|     | 3.  | . 1 |    |    | 概述         |                     | 18 |

|     | 3.  | . 2 |    |    | 程序存储       | 型<br>品              | 18 |

|     |     |     | 3. | 2  | . 1        | 慨述                  | 18 |

|     |     |     | 3. | 2  | . 2        | 程序区地址映射示意图          | 18 |

|     |     |     | 3. | 2  | . 3        | 程序计数器(PC)           | 18 |

|     |     |     | 3. | 2  | . 4        | 程序堆栈                | 19 |

|     |     |     | 3. | 2  | . 5        | 程序存储器查表操作           | 20 |

|     |     |     |    |    | 3. 2. 5. 1 | 概述                  | 20 |

|     |     |     |    |    | 3. 2. 5. 2 | 操作例程                | 20 |

|     |     |     | 3. | 2  | . 6        | 特殊功能寄存器             | 20 |

|     | 3.  | . 3 |    |    | 数据存储       | 면<br>m              | 22 |

|     |     |     | 3. | 3. | . 1        | 慨述                  | 22 |

|     |     |     | 3. | 3. | . 2        | 数据区地址映射             | 22 |

|     |     |     | 3. | 3. | . 3        | 通用数据存储器             | 22 |

|     |     |     | 3. | 3. | . 4        | 特殊功能寄存器             | 22 |

|     |     |     | 3. | 3. | . 5        | 寻址方式                | 23 |

|     |     |     |    |    | 3. 3. 5. 1 | 直接寻址                | 23 |

|     |     |     |    |    | 3. 3. 5. 2 | 间接寻址                | 24 |

|     |     |     | 3. | 3. | . 6        | <b>恃殊功能寄存器</b>      | 25 |

|     | 3.  | . 4 |    |    | EEPROM     | 存储器                 | 26 |

|     |     |     | 3. | 4. | . 1        | 既述                  | 26 |

|     |     |     | 3. | 4. | . 2        | 详细操作说明              | 26 |

| 第 4 | 阜   | Í   |    |    | 输入/输出      | 端口                  | 30 |

|     | 4   | . 1 |    |    | 概述         |                     | 30 |

|     | 4.  | . 2 |    |    | 结构框图       |                     | 30 |

|     | 4.  | . 3 |    |    | I/O 端口5    | <b>b能设置</b>         | 31 |

|     |     |     |    |    |            |                     |    |

|     |      | 4. | 3. | 1          | I/O 端口输入/输出控制                | 31   |

|-----|------|----|----|------------|------------------------------|------|

|     |      | 4. | 3. | 2          | I/O 端口弱上拉、弱下拉功能              | 31   |

|     |      | 4. | 3. | 3          | I/O 端口复用功能                   | 31   |

|     | 4. 4 |    |    | 端口中断       |                              | 32   |

|     |      | 4. | 4. | 1          | 按键中断(KINT)                   | 32   |

|     |      | 4. | 4. | 2          | 外部端口中断(PINT)                 | 32   |

|     | 4. 5 | ,  |    | I/O 端口排    | 操作注意事项                       | 32   |

|     | 4. 6 | ;  |    | 特殊功能       | 寄存器                          | 33   |

| 第 5 | 章    |    |    | 特殊功能       | 及操作特性                        | 36   |

|     | 5. 1 |    |    | 系统时钟       | 与振荡器                         | 36   |

|     |      | 5. | 1. | 1          | 概述                           | 36   |

|     |      | 5. | 1. | 2          | 时钟源                          | 36   |

|     |      |    |    | 5. 1. 2. 1 | 外部时钟                         | 37   |

|     |      |    |    | 5. 1. 2. 2 | 内部高速 16MHz RC 振荡器模式(INTOSCH) | . 37 |

|     |      |    |    | 5. 1. 2. 3 | 内部低速 32kHz RC 振荡器模式(INTOSCL) | . 37 |

|     |      | 5. | 1. | 3          | 系统时钟切换                       | 38   |

|     |      |    |    | 5. 1. 3. 1 | 系统上电时序                       | 39   |

|     |      |    |    | 5. 1. 3. 2 | 系统时钟切换时序                     | 39   |

|     |      | 5. | 1. | 4          | 系统时钟分频                       | 41   |

|     |      | 5. | 1. | 5          | 特殊功能寄存器                      | 41   |

|     | 5. 2 |    |    | 看门狗定       | 时器                           | 44   |

|     |      | 5. | 2. | 1          | 概述                           | 44   |

|     |      | 5. | 2. | 2          | 内部结构图                        | 44   |

|     |      | 5. | 2. | 3          | WDT 定时器                      | 44   |

|     |      | 5. | 2. | 4          | 特殊功能寄存器                      | 45   |

|     | 5. 3 | }  |    | 复位模块       |                              | 46   |

|     |      | 5. | 3. | 1          | 概述                           | 46   |

|     |      | 5. | 3. | 2          | 上电复位                         | 46   |

|     |      | 5. | 3. | 3          | 下电复位                         | 46   |

|     |      | 5. | 3. | 4          | 外部 N_MRST 管脚复位               | 47   |

|     |      | 5. | 3. | 5          | 看门狗定时器溢出复位                   | 48   |

|     |      | 5. | 3. | 6          | RST 指令复位                     | 49   |

|     |      | 5. | 3. | 7          | 特殊功能寄存器                      | 49   |

|     | 5. 4 |    |    | 低功耗操       | 作                            | 51   |

|     |      | 5. | 4. | 1          | MCU 低功耗模式                    | 51   |

|     |      | 5. | 4. | 2          | 低功耗模式配置                      | 51   |

|     |      | 5. | 4. | 3          | IDLE 唤醒方式配置                  | 51   |

|     |      | 5. | 4. | 4          | 唤醒时序图                        | 52   |

|     |      | 5. | 4. | 5          | 特殊功能寄存器                      | 53   |

| 第6  | 章    |    |    | 外设         |                              | 54   |

|     | 6. 1 |    |    | 定时器/计      | ├数器模块(Timer/Counter)         | . 54 |

|     |      | 6. | 1. | 1          | 8 位定时器/计数器(T8N)              | . 54 |

|     |      |    |    | 6. 1. 1. 1 | 概述                           | 54   |

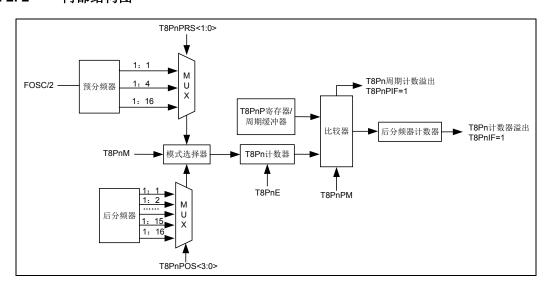

|     |      |    |    | 6. 1. 1. 2 | 内部结构图                        | 54   |

|      |     |      |    | 6. 1. 1. 3 工作模式               | 54 |

|------|-----|------|----|-------------------------------|----|

|      |     |      |    | 6. 1. 1. 4 预分频器               | 55 |

|      |     |      |    | 6. 1. 1. 5 工作模式               | 55 |

|      |     |      |    | 6. 1. 1. 6 定时器模式              | 55 |

|      |     |      |    | 6. 1. 1. 7 同步计数器模式            | 56 |

|      |     |      |    | 6. 1. 1. 8 特殊功能寄存器            | 57 |

|      |     | 6.   | 1. | 2 两路 8 位 PWM 时基定时器(T8P1/T8P2) | 58 |

|      |     |      |    | 6. 1. 2. 1 概述                 | 58 |

|      |     |      |    | 6. 1. 2. 2 内部结构图              | 58 |

|      |     |      |    | 6. 1. 2. 3 工作模式               | 58 |

|      |     |      |    | 6. 1. 2. 4 预分频器和后分频器          | 59 |

|      |     |      |    | 6. 1. 2. 5 工作模式               | 60 |

|      |     |      |    | 6. 1. 2. 6 定时器模式              | 60 |

|      |     |      |    | 6. 1. 2. 7 PWM 输出模式           | 60 |

|      |     |      |    | 6. 1. 2. 8 特殊功能寄存器            | 62 |

| 6    | . 2 |      |    | 低电压检测模块(LVD0/LVD1)            | 65 |

|      |     | 6.   | 2. | 1 概述                          | 65 |

|      |     | 6.   | 2. | 2 LVD 操作                      | 65 |

|      |     | 6.   | 2. | 3 特殊功能寄存器                     | 66 |

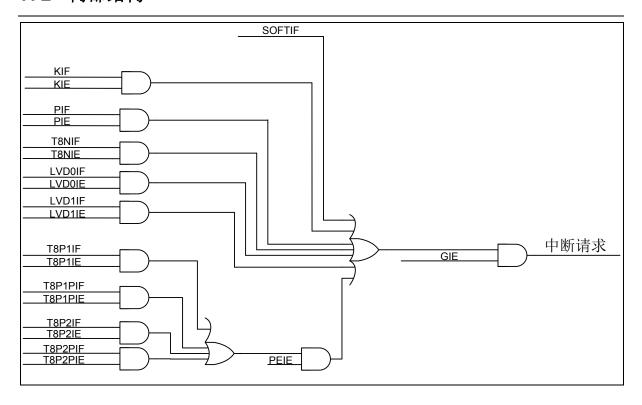

| 第7章  | 〕   |      |    | 中断处理                          | 67 |

| 7    | . 1 |      |    | 概述                            | 67 |

| 7    | . 2 |      |    | 内部结构                          | 67 |

| 7    | . 3 |      |    | 中断模式选择                        | 67 |

|      |     | 7.   | 3. | 1 默认中断模式                      |    |

|      |     | 7.   | 3. | 2 向量中断模式                      | 68 |

| 7    | . 4 |      |    | 中断现场保护                        | 69 |

| 7    | . 5 |      |    | 中断操作                          | 69 |

|      |     | 7.   | 5. | 1 外部中断                        | 69 |

|      |     | 7.   | -  | 7 1 11 12 17 2 1 17 1         | 70 |

|      |     | 7.   | 5. |                               |    |

|      |     | 7.   | 5. | 4 T8Pn(T8P1/T8P2)定时中断         | 70 |

|      |     | 7.   | 5. |                               |    |

|      |     | 7.   | 5. | 6 LVDn 中断                     | 70 |

|      |     | 7.   |    | 1 410/11 122.1                |    |

| 7    | . 6 |      |    | 特殊功能寄存器                       | 71 |

| 第8章  | 章   |      |    | 芯片配置字                         | 75 |

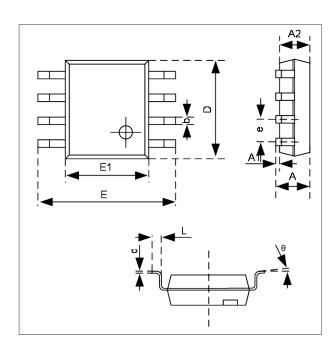

| 第9章  | 重   |      |    | 芯片封装图                         |    |

| 9    | . 1 |      |    | 8-pin SOP 封装图                 | 76 |

| 附录 1 | 1   |      |    | 指令集                           |    |

| 附    | 付录  | : 1. | 1  |                               |    |

| 附    | 付录  | : 1. | 2  | * ** *** *** *** ***          |    |

| 附    | 付录  | : 1. | 3  | — · · · · · · · · ·           |    |

| 附    | 付录  | : 1. |    |                               |    |

| 附录 2 | 2   |      |    | 特殊功能寄存器总表                     | 81 |

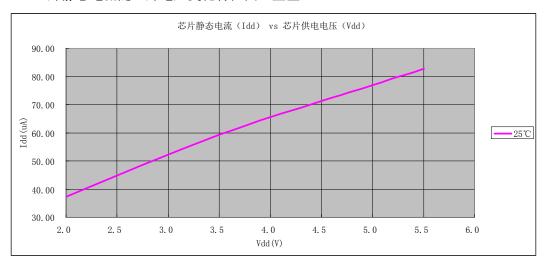

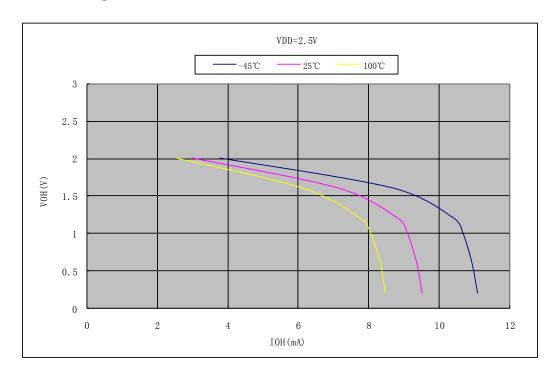

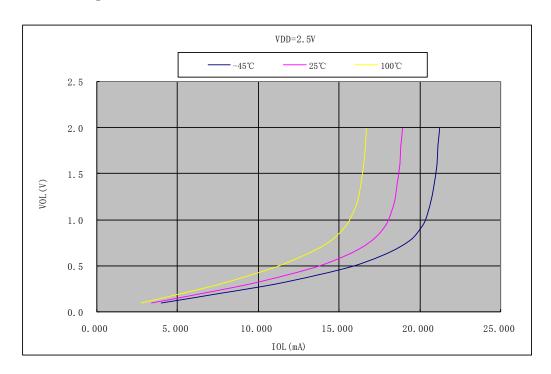

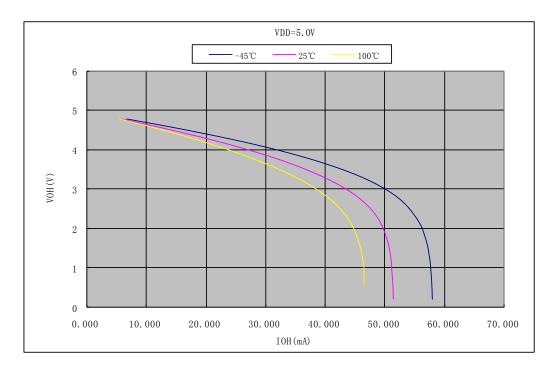

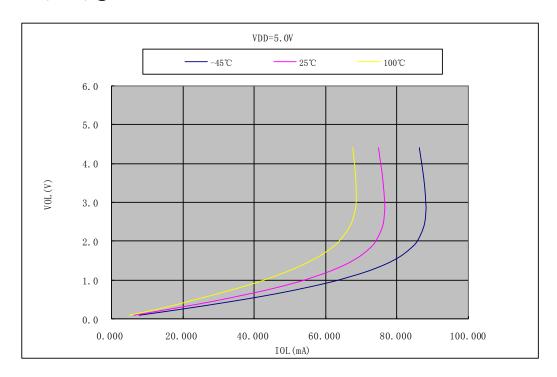

| 附录 3    | 电气特性           | 86 |

|---------|----------------|----|

|         | 多数特性表          |    |

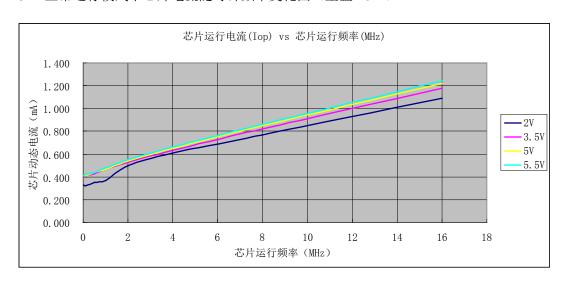

| 附录 3. 2 | 参数特性图          | 89 |

| 附录 4    | 内部 EEPROM 电气特性 | 94 |

| 附录 4. 1 | 直流电气特性表        | 94 |

| 附录 4.2  | 交流电气特性表        | 94 |

## 图目录

| 图 | 1-1  | HR7P159BE2SA 结构框图                          | 13 |

|---|------|--------------------------------------------|----|

| 图 | 1-2  | HR7P159BE2SA(SOP8)顶视图                      | 13 |

| 图 | 3-1  | 程序区地址映射                                    | 18 |

| 图 | 3-2  | 堆栈示意图                                      | 20 |

| 图 | 3-3  | 数据区地址映射示意图                                 | 22 |

| 图 | 3-4  | 特殊功能寄存器空间                                  | 23 |

| 图 | 3-5  | 普通直接寻址示意图                                  | 24 |

| 图 | 3-6  | 间接寻址示意图                                    | 24 |

| 图 | 4-1  | 输入/输出端口结构图——PA0/PA2/PA3/PBx                | 30 |

| 图 | 4-2  | 输入端口结构图——PA1                               | 31 |

| 图 | 5-1  | 系统时钟内部结构图                                  | 36 |

| 图 | 5-2  | 晶体/陶瓷振荡器模式(HS、XT、LP 模式)                    | 37 |

| 图 | 5-3  | 系统上电时序图                                    |    |

| 图 | 5-4  | INTOSCL 时钟切换到 INTOSCH/HS/XT 时钟             | 39 |

| 图 | 5-5  | INTOSCH/HS/XT 时钟切换到 INTOSCL 时钟             | 40 |

| 图 | 5-6  | 低速 LP 时钟切换到 INTOSCH 时钟                     | 40 |

| 图 | 5-7  | INTOSCH 时钟切换到低速 LP 时钟                      | 41 |

| 图 | 5-8  | 看门狗定时器内部结构图                                | 44 |

| 图 | 5-9  | 芯片复位原理图                                    | 46 |

| 图 | 5-10 | 上电复位时序示意图                                  | 46 |

| 图 | 5-11 | 下电复位时序示意图                                  | 47 |

| 图 | 5-12 | 外部 N_MRST 管脚复位                             | 47 |

| 图 | 5-13 | N_MRST 复位参考电路图 1                           | 48 |

| 图 | 5-14 | N_MRST 复位参考电路图 2                           | 48 |

| 图 | 5-15 | 看门狗溢出复位                                    | 49 |

| 图 | 5-16 | RST 指令复位                                   | 49 |

| 图 | 5-17 | HS/XT/INTOSCO/INTOSC 模式时,系统唤醒 IDLE0 时序图    | 53 |

| 图 | 5-18 | LP 模式时,系统唤醒 IDLE0 时序图                      | 53 |

| 图 | 5-19 | HS/XT/INTOSCO/INTOSC/LP 模式时,系统唤醒 IDLE1 时序图 | 53 |

| 图 | 6-1  | T8N 内部结构图                                  | 54 |

| 图 | 6-2  | 定时器模式时序图                                   | 56 |

| 图 | 6-3  | 计数器模式时序图(T8NEG=0,T8NCKI上升沿计数)              | 56 |

| 图 | 6-4  | T8P1/T8P2 内部结构图                            | 58 |

| 图 | 6-5  | T8Pn 定时器模式时序图                              | 60 |

| 图 | 6-6  | T1n PWM 模式示意图                              | 61 |

| 图 | 6-7  | PWM 输出示意图                                  | 61 |

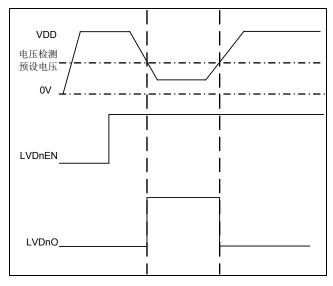

| 图 | 6-8  | LVD 工作时序图                                  | 65 |

| 图 | 7-1  | 中断控制逻辑                                     | 67 |

## 表目录

| 表 | 1-1 | 管脚说明              | .15 |

|---|-----|-------------------|-----|

| 表 | 4-1 | I/O 端口弱上拉         | 31  |

| 表 | 4-2 | I/O 端口弱下拉         | 31  |

| 表 | 4-3 | 按键中断              | 32  |

| 表 | 4-4 | 外部端口中断            | 32  |

| 表 | 5-1 | 晶体振荡器电容参数参考表      | 37  |

| 表 | 5-2 | 振荡模式切换选择          | 39  |

| 表 | 5-3 | 下电复位电压点配置表        | 47  |

| 表 | 5-4 | 低功耗模式配置表          | 51  |

| 表 | 5-5 | 休眠唤醒表             | 52  |

| 表 | 5-6 | 休眠唤醒时间表           | 52  |

| 表 | 6-1 | T8N 工作模式配置表       | 55  |

| 表 | 6-2 | T8N 预分频器配置表       | 55  |

| 表 | 6-3 | T8Pn 工作模式配置表      | 59  |

| 表 | 6-4 | T8P1/T8P2 预分频器配置表 | 59  |

| 表 | 6-5 | T8P1/T8P2 后分频器配置表 | 59  |

| 表 | 7-1 | 中断处理模式配置表         | 67  |

| 表 | 7-2 | 默认中断模式中断逻辑表       | 68  |

| 表 | 7-3 | 向量中断模式中断逻辑表       | 69  |

## 第1章 芯片简介

## 1.1 概述

#### ◆ 内核

- ◇ 高性能哈佛型 RISC CPU 内核

- ◇ 79条精简指令

- ◇ 指令周期为2个系统时钟周期

- ◇ 复位向量位于 000<sub>H</sub>,中断向量位于 008<sub>H</sub>

- ◇ 支持中断处理,10个中断源,支持中断向量表

- ◇ CPU 最高工作频率

- 2MHz (VDD=2.1~5.5V)

- 20MHz (VDD=3.0~5.5V)

#### ◆ 存储资源

- ◇ 992 Words OTP 程序存储器, 8 级程序堆栈

- ◇ 256 Bytes 的 EERPOM 数据存储器

- ◇ 128 Bytes SRAM 数据存储器

- ◇ 程序存储器支持直接寻址、相对寻址和查表读操作

- ◇ 数据存储器支持直接寻址和间接寻址

#### ◆ I/O 端口

- ◇ 最多支持 5 个 I/O 和 1 个输入

- PA 端口 (PA0~PA3)

- PB 端口 (PB0~PB1)

- ◇ 支持 1 个外部端口中断 PINT (PINTO 为输入端)

- ◇ 支持 1 个 5 输入外部按键中断 KINT (KIN0~KIN4 为输入端)

- ◇ 支持独立的可配置内部弱上/下拉输入端口

- 常温下,弱上下拉电阻匹配精度在±3%以内(VDD=5V)

#### ◆ 复位及时钟

- ◇ 内嵌上电复位电路 POR

- ◇ 内嵌下电复位电路 BOR

- ◇ 内嵌低电压检测中断电路

- ◇ 支持外部复位

- ◇ 支持独立硬件看门狗定时器

- ◇ 支持内部高频 16MHz RC 振荡时钟源

- 可分频, 最低可分频至 32KHz

- 出厂前,芯片已经在常温 25℃条件下校准,校准精度为±2%

- ◇ 支持内部低频 32KHz RC 振荡器时钟源(用于 WDT 时钟源及可配置为系统时钟源)

- ◇ 支持外部振荡器时钟源

V1.4 11/95

- ◇ 支持高低速系统时钟切换

- 内部低频 32KHz 时钟与内/外部高频时钟切换

- 外部低频时钟与内部高频时钟切换

#### ◆ 外设

- ◇ 8 位定时器 T8N

- 定时器模式(系统时钟)/计数器模式(外部计数时钟输入)

- 支持可配置预分频器

- 支持中断产生

- ◇ 8 位 PWM 时基定时器 T8P1/T8P2

- 定时器模式(系统时钟)

- 支持可配置预分频器及可配置后分频器

- 支持两路脉宽调制 (PWM) 输出扩展功能, PWM 输出精度最大为 9 位

- 支持中断产生

- ◇ 两路独立的低电压检测电路 LVD0/LVD1

- 支持 8 种可配置电压检测,分别是 2.1V/2.4V/3.0V/3.2V/3.6V/3.8V/4.1V/检测外部 LVDIN

- 支持中断产生

- ◆ 编程及调试接口

- ◇ 支持 ICD 调试

- ◇ 支持编程代码加密保护

- ◆ 设计工艺及封装

- ◇ 低功耗、高速 OTP CMOS 工艺

- ◇ 8个管脚,采用 SOP 封装

- ◆ 工作条件

- ◇ 工作电压范围: 2.1V~5.5V

- ◇ 工作温度范围: -40℃~85℃

## 1.2 应用领域

本芯片可用于 LED 灯控、便携式产品和小家电等领域。

12/95

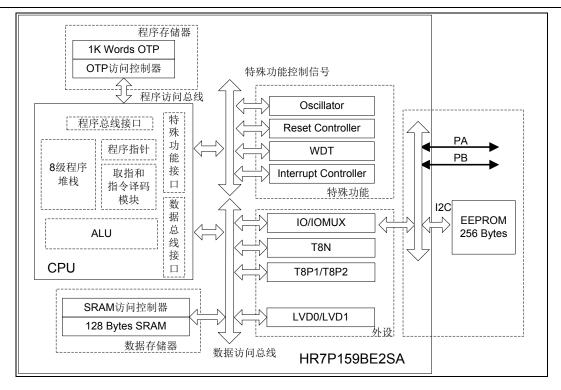

## 1.3 结构框图

图 1-1 HR7P159BE2SA 结构框图

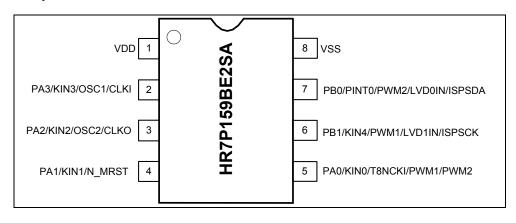

## 1.4 管脚分配图

## 1. 4. 1 8-pin

图 1-2 HR7P159BE2SA (SOP8) 顶视图

- 注 1: N\_MRST 表示低电平复位有效;

- 注 2: T8P1 的 PWM1 输出端口可软件配置。

- 注 3: T8P2 的 PWM2 输出端口可软件配置。

- 注 4: 用户系统必须保证 N\_MRST 管脚电压低于芯片电源电压 VDD, 否则芯片可能进入异常工作模式。如果该管脚上电压存在过冲,则用户系统必须限制该脉冲的电压不高于 VDD+0.5V,脉冲宽度不超过 100us。

V1.4 13/95

## 1.4.2 管脚复用说明

| 管脚名                              | 管脚复用   | 输入类型  | 输出类型 | A/D | 端口说明            | 备注                 |  |  |

|----------------------------------|--------|-------|------|-----|-----------------|--------------------|--|--|

|                                  | PA0    | TTL   | CMOS | D   | 通用 I/O          |                    |  |  |

|                                  | KIN0   | TTL   | _    | D   | 外部按键中断输入 0      |                    |  |  |

| PA0/KIN0/T8NCKI/                 | T8NCKI | TTL   | _    | D   | T8N 时钟输入        | 可单独使               |  |  |

| PWM1/PWM2                        | PWM1   | _     | CMOS | D   | T8P1 为时基的脉宽调制输出 | 能弱上/下<br>拉         |  |  |

|                                  | PWM2   | _     | CMOS | D   | T8P2 为时基的脉宽调制输出 |                    |  |  |

|                                  | PA1    | TTL   | CMOS | D   | 通用              |                    |  |  |

| PA1/KIN1/N_MRST                  | KIN1   | TTL   | _    | D   | 外部按键中断输入 1      | 可单独使<br>能弱上拉       |  |  |

|                                  | N_MRST | TTL   | _    | D   | 外部复位输入          | 11099 7717         |  |  |

|                                  | PA2    | TTL   | CMOS | D   | 通用 I/O          |                    |  |  |

| PA2/KIN2/OSC2/CLKO               | KIN2   | TTL   | _    | D   | 外部按键中断输入2       | 可单独使<br>能弱上/下      |  |  |

| 1 AZ/KINZ/OOOZ/OLKO              | OSC2   | _     | osc  | Α   | 晶振/谐振器输出        | 拉                  |  |  |

|                                  | CLKO   | _     | CMOS | D   | Fosc/16 参考时钟输出  |                    |  |  |

|                                  | PA3    | TTL   | CMOS | D   | 通用 I/O          | 可单独使<br>能弱上/下<br>拉 |  |  |

|                                  | KIN3   | TTL   | _    | D   | 外部按键中断输入3       |                    |  |  |

| PA3/KIN3/OSC1/CLKI               | OSC1   | osc   | _    | Α   | 晶振/谐振器输入        |                    |  |  |

|                                  | CLKI   | TTL   | _    | A/D | 时钟输入            |                    |  |  |

|                                  | PB0    | TTL   | CMOS | D   | 通用 I/O          |                    |  |  |

|                                  | PINT0  | TTL   | _    | D   | 外部端口中断输入0       |                    |  |  |

| PB0/PINT0/PWM2/<br>LVD0IN/ISPSDA | PWM2   |       | CMOS | D   | T8P2 为时基的脉宽调制输出 | 可单独使<br>能弱上/下<br>拉 |  |  |

|                                  | LVD0IN | AN    | _    | Α   | LVD0 检测输入电压     | 17.7.              |  |  |

|                                  | ISPSDA | TTL   | CMOS | D   | 串行编程数据输入输<br>出  |                    |  |  |

|                                  | PB1    | TTL   | CMOS | D   | 通用 I/O          |                    |  |  |

|                                  | KIN4   | TTL   | _    | D   | 外部按键中断输入4       |                    |  |  |

| PB1/KIN4/PWM1/<br>LVD1IN/ISPSCK  | PWM1   | _     | CMOS | D   | T8P1 为时基的脉宽调制输出 | 可单独使<br>能弱上/下<br>拉 |  |  |

|                                  | LVD1IN | AN    | _    | Α   | LVD1 检测输入电压     |                    |  |  |

|                                  | ISPSCK | TTL   | _    | D   | 串行编程时钟输入        |                    |  |  |

| VDD                              | VDD    | Power | _    | _   | 电源              | _                  |  |  |

| 管脚名 | 管脚复用 | 输入类型  | 输出类型 | A/D | 端口说明             | 备注 |

|-----|------|-------|------|-----|------------------|----|

| VSS | VSS  | Power |      |     | 地, <b>0V</b> 参考点 | _  |

表 1-1 管脚说明

注 1: A = 模拟端口, D = 数字端口;

所有通用数据 I/O 均为 TTL 施密特输入和 CMOS 输出驱动。

OSC: 晶振输入输出 Power: 电源输入输出

AN: 模拟输入

注 2: N\_MRST 表示低电平有效;

注 3: T8P1 的 PWM1 输出端口可软件配置; 注 4: T8P2 的 PWM2 输出端口可软件配置。

## 1.4.3 管脚参数对照表

| 管脚名                          | HR7P159BE2SA |

|------------------------------|--------------|

| <b></b>                      | SOP8         |

| PA0/KIN0/T8NCKI/PWM1/ PWM2   | 5            |

| PA1/KIN1/N_MRST              | 4            |

| PA2/KIN2/OSC2/CLKO           | 3            |

| PA3/KIN3/OSC1/CLKI           | 2            |

| PB0/PINT0/PWM2/LVD0IN/ISPSDA | 7            |

| PB1/KIN4/PWM1/LVD1IN/ISPSCK  | 6            |

| VDD                          | 1            |

| VSS                          | 8            |

## 1. 4. 4 MCU与EEPROM内部连线关系

| 内部 EEPROM(I/O) | 内部 MCU(I/O) | 说明           |

|----------------|-------------|--------------|

| SDA (I/O)      | PB3 (I/O)   | I2C 数据线      |

| SCL (I)        | PB2 (O)     | I2C 时钟线      |

| WP (I)         | VSS         | 固定接低电平,可正常读写 |

| VDD            | VDD         | EEPROM 的电源   |

- 注 1: I = 数字输入, O = 数字输出, I/O = 数字输入/输出;

- 注 2: 建议对内部 EEPROM 的操作速度不要太快,如果整机供电电压比较低,SCL 的速度也要相应降低,才能保证可靠读写。推荐工作电压 3~5V 范围内,SCL 的读写操作频率不超过 150KHZ。

- 注 3: 内部 EEPROM 的 SDA 作为输入时,内部上拉电阻初始化后一定要使能。

## 第2章 内核特性

## 2.1 CPU内核概述

#### ◇ 内核特性

- 高性能哈佛型 RISC CPU 内核

- 79 条精简指令

- 系统时钟工作频率最高为 20MHz

- 机器周期为2个系统时钟周期

- 支持中断处理和中断向量表

## 2.2 系统时钟和机器周期

系统时钟频率(Fosc)最高支持 16MHz。两个系统时钟周期通过片内时钟生成器产生两个不重叠的正交时钟 phase1 (p1), phase2 (p2)。

两个不重叠的正交时钟周期组成一个机器周期。若系统时钟频率为 **4MHz**,一个机器周期的时间为 **500ns**。

## 2.3 指令集概述

采用 HR7P 系列 79 条精简指令集系统。

除部分条件跳转与控制程序流程的指令为双(机器)周期指令外,其他指令均为单(机器)周期指令。具体指令集请参考《附录 1 指令集》。

## 2.4 特殊功能寄存器

CPU 相关寄存器包括 10-bit 程序计数器 PCRL/PCRH,程序状态字寄存器 PSW 和累加器 A 寄存器 AREG。其中程序状态寄存器 PSW 用于存放各个状态标志位,包括程序出栈/压栈溢出、负数标志位、溢出标志位、零标志位、半进位/半借位标志位,以及全进位或全借位标志位等。

| PSW: 程序状态字寄存器 |   |    |    |     |     |     |     |     |  |  |

|---------------|---|----|----|-----|-----|-----|-----|-----|--|--|

| Bit           | 7 | 6  | 5  | 4   | 3   | 2   | 1   | 0   |  |  |

| Name          | _ | UF | OF | N   | OV  | Z   | DC  | С   |  |  |

| R/W           | _ | R  | R  | R/W | R/W | R/W | R/W | R/W |  |  |

| POR           | Х | 0  | 0  | Х   | Х   | х   | Х   | Х   |  |  |

"x": 未知

Bit 7 未使用

Bit 6 UF: 程序出栈溢出标志位

0:程序出栈未溢出1:程序出栈溢出

Bit 5 OF:程序压栈溢出标志位

0:程序压栈未溢出 1:程序压栈溢出

Bit 4 N: 负数标志位

V1.4 16/95

0: 有符号算术或逻辑运算结果为正数

1: 结果为负数

Bit 3 OV: 溢出标志位

0: 有符号算术运算未发生溢出

1: 发生溢出

Bit 2 Z: 零标志位

0: 算术或逻辑运算的结果不为零

1: 算术或逻辑运算的结果为零

Bit 1 DC: 半进位或半借位标志位

0: 低四位无进位或低四位有借位

1: 低四位有进位或低四位无借位

Bit 0 C: 全进位或全借位标志位

0: 无进位或有借位

1: 有进位或无借位

- 注 1: 仅部分指令可对 PSW 寄存器进行写操作,包括 JDEC、JINC、SWAP、BCC、BSS、BTT、MOVA 和 SETR。 其它指令对 PSW 寄存器的写操作,只根据运行结果影响相应状态标志位。

- 注 2: OF 和 UF 位为只读标志位,仅上电复位、复位指令和 N\_MRST 复位会将其清零,其他复位不影响该两位标志位。

| AREG: 累加器 A 寄存器 |     |           |     |     |     |     |     |     |  |

|-----------------|-----|-----------|-----|-----|-----|-----|-----|-----|--|

| Bit             | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

| Name            |     | AREG<7:0> |     |     |     |     |     |     |  |

| R/W             | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| POR             | х   | Х         | Х   | Х   | Х   | Х   | Х   | х   |  |

"x": 未知

Bit 7~0 AREG<7:0>: 累加器的值

| PCRL: 程序计数器低 8 位 |     |          |     |     |     |     |     |     |  |  |

|------------------|-----|----------|-----|-----|-----|-----|-----|-----|--|--|

| Bit              | 7   | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name             |     | PCR<7:0> |     |     |     |     |     |     |  |  |

| R/W              | R/W | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR              | 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

Bit 7~0 PCR<7:0>: 程序计数器低 8 位

| PCRH: 和 | PCRH: 程序计数器高 2 位 |   |   |   |   |   |      |       |  |  |  |  |

|---------|------------------|---|---|---|---|---|------|-------|--|--|--|--|

| Bit     | 7                | 6 | 5 | 4 | 3 | 2 | 1    | 0     |  |  |  |  |

| Name    | _                | _ | _ | _ | _ | _ | PCR. | <9:8> |  |  |  |  |

| R/W     | _                | _ | _ | _ | _ | _ | R/W  | R/W   |  |  |  |  |

| POR     | 0                | 0 | 0 | 0 | 0 | 0 | 0    | 0     |  |  |  |  |

Bit 7~2 未使用

Bit 1~0 PCR<9:8>: 程序计数器高 2 位

## 第3章 存储资源

## 3.1 概述

本芯片采用哈佛总线架构,程序寻址空间和数据寻址空间相互独立。

片内存储器资源包括:

- ◇ 992 Words OTP 程序存储器;

- ◇ 128 字节 SRAM

其中 OTP 程序存储器被映射到程序寻址空间, SRAM 数据存储器被映射到数据寻址空间。

## 3.2 程序存储器

## 3. 2. 1 概述

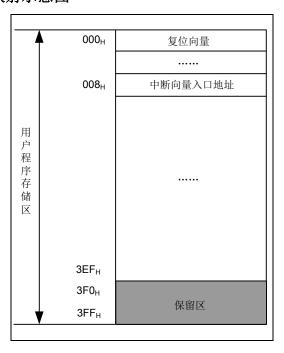

OTP 程序存储器用于存储用户程序。由于芯片指令位宽为 16 位(2 个字节),因此 992 Words OTP 程序存储器被映射到程序寻址空间为 000<sub>H</sub>~3EF<sub>H</sub>,其中 3F0<sub>H</sub>~3FF<sub>H</sub>为保留区。每个访问地址对应 16 位宽(2 个字节)的存储单元。通过 10 位程序计数器 PC 进行程序寻址访问。

复位向量位于 000H, 中断向量入口地址位于 008H, 支持 8 级硬件堆栈。

## 3.2.2 程序区地址映射示意图

图 3-1 程序区地址映射

## 3.2.3 程序计数器 (PC)

程序计数器中存放的是要执行的下一条指令的地址。PC 在每个指令周期后都会自动加 1,除非 PC 的值被指令或中断异常改写。10 位程序计数器 PC<9:0>,无实际物理地址,不可读写,可寻址 1K 程序存储空间 000<sub>H</sub>~3FF<sub>H</sub>,超出地址范围会导致 PC 循环(又从 000<sub>H</sub>

V1.4 18/95

开始访问)。PC<7:0>可通过 PCRL 寄存器的读/写操作进行读/写,而 PC<9:8>通过 PCRH 寄存器来间接(如 RCALL、CALL、GOTO 等指令)赋值。

芯片复位时, PCRL、PCRH 和 PC 都会被清零。PC 硬件堆栈操作不会影响 PCRH 的值。

#### 注: 各种指令对 PC 的影响:

- 1. 通过指令直接修改 PC 值时,对 PCRL 为目标寄存器的操作可直接修改 PC<7:0>,即 PC<7:0>=PCRL<7:0>; 而操作 PC<7:0>的同时也会执行 PC<9:8>=PCRH<1:0>,因此,修改 PC 时,应先修改 PCRH<1:0>,再修 改 PCRL<7:0>。

- 2. 执行 RCALL 指令时, PC<7:0>为寄存器 R 中的值; 而 PC<9:8> =PCRH<1:0>。

- 3. 执行 CALL, GOTO 指令时, PC<9:0>为指令中 11 位立即数的低 10 位(操作数)。

- 4. 执行 LCALL 指令时,该指令为双字指令共有 16 位立即数(操作数)。PC<9:0>被修改为该 16 位立即数的值的低 10 位;同时 PCRH<1:0>被修改为 I<9:8>的值。

- 5 执行 AJMP 指令时,该指令为双字指令共有 16 位立即数(操作数)。PC<9:0> 被修改为该 16 位立即数的值 低 10 位,同时 PCRH 修改为 I<9:8>的值。

- 6. 执行 PAGE 指令时,PCRH<7:3>的值将被该指令的立即数替换(程序存储器的大小只有 1008 Words,因此 PCRH<7:3>被固定为全零,执行 PAGE 指令后 PC 值不受影响)。

- 7. 执行其他指令时, PC 值自动加 1。

## 应用实例:以 PCRL 为目标寄存器的指令应用程序

. . . . . .

MOVI pageaddr

MOVA PCRH ; 设置表格页面地址

MOVI tableaddr ; 设置偏移量给 A 寄存器

CALL TABLE ; 调用子程序方式查表

. . . . . .

TABLE:

ADD PCRL, F ; PC 加上偏移量,指向访问的地址

RETIA 0X01 RETIA 0X02 RETIA 0X03

. . . . . .

## 3.2.4 程序堆栈

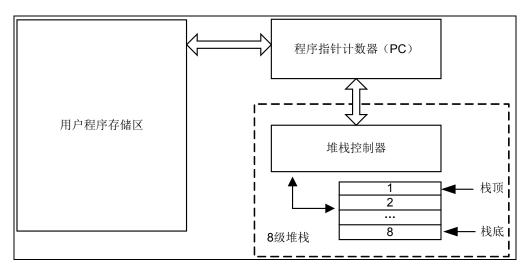

芯片内有 8 级程序堆栈(硬件堆栈),堆栈位宽与 PC 位宽相等,用于 PC 的压栈和出栈。 执行 CALL、LCALL 和 RCALL 指令或中断被响应后,PC 自动压栈保护;当执行 RET、 RETIA 或 RETIE 指令时,堆栈会将最近一次压栈的值返回至 PC。

程序堆栈只支持8级缓冲操作,即程序堆栈只保存最近的8次压栈值,对于连续超过8次的压栈操作,第9次的压栈数据使得第1次的压栈数据丢失。同样,超过8次的连续出栈,第9次出栈操作,可能使得程序流程不可控。芯片复位后,堆栈指针将重新指向堆栈顶部。

图 3-2 堆栈示意图

## 3.2.5 程序存储器查表操作

## 3. 2. 5. 1 概述

程序存储器查表操作只支持查表读操作。

查表读操作通过查表读指令将 FRA(FRAH,FRAL)所指向的程序存储器地址中的一个字(Word)读入 ROMD(ROMDH,ROMDL)中。

;读取程序存储器 0105<sub>H</sub>

## 3. 2. 5. 2 操作例程

## 应用例程 1:程序存储器查表读。

MOVI 0x05 MOVA FRAL MOVI 0X01 MOVA FRAH

TBR

MOV ROMDH, 0

... ...

MOV ROMDL, 0

... ...

## 3.2.6 特殊功能寄存器

| FRAL: 查表地址寄存器低 8 位 |     |          |     |     |     |     |     |     |  |  |

|--------------------|-----|----------|-----|-----|-----|-----|-----|-----|--|--|

| Bit                | 7   | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name               |     | FRA<7:0> |     |     |     |     |     |     |  |  |

| R/W                | R/W | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR                | Х   | х        | Х   | Х   | Х   | Х   | Х   | Х   |  |  |

"x": 未知

Bit 7~0 FRA<7:0>: 查表地址低 8 位

| FRAH: 결 | FRAH: 查表地址寄存器高 8 位 |           |     |     |     |     |     |     |  |  |

|---------|--------------------|-----------|-----|-----|-----|-----|-----|-----|--|--|

| Bit     | 7                  | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name    |                    | FRA<15:8> |     |     |     |     |     |     |  |  |

| R/W     | R/W                | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR     | Х                  | Х         | Х   | Х   | Х   | Х   | Х   | Х   |  |  |

**"x"**: 未知

Bit 7~0 FRA<15:8>: 查表地址高 8 位

| ROMDL: 查表数据寄存器低 8 位 |     |           |     |     |     |     |     |     |  |

|---------------------|-----|-----------|-----|-----|-----|-----|-----|-----|--|

| Bit                 | 7   | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |

| Name                |     | ROMD<7:0> |     |     |     |     |     |     |  |

| R/W                 | R/W | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |

| POR                 | Х   | Х         | Х   | Х   | Х   | Х   | Х   | Х   |  |

"x": 未知

Bit 7~0 ROMD<7:0>: 查表数据低 8 位

| ROMDH: | 查表数据 | 查表数据寄存器高8位 |     |     |     |     |     |     |  |  |  |

|--------|------|------------|-----|-----|-----|-----|-----|-----|--|--|--|

| Bit    | 7    | 6          | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| Name   |      | ROMD<15:8> |     |     |     |     |     |     |  |  |  |

| R/W    | R/W  | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| POR    | Х    | Х          | Х   | Х   | Х   | Х   | Х   | Х   |  |  |  |

"x": 未知

Bit 7~0 ROMD<15:8>: 查表数据高 8 位

## 3.3 数据存储器

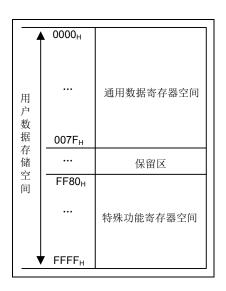

## 3.3.1 概述

- ◇ 数据存储器由2部分组成

- 通用数据存储器 GPR

- 特殊功能寄存器 SFR

- ◇ 通用数据存储器 GPR

- 共1个存储体组

- 128 字节,地址范围 00<sub>H</sub>~7F<sub>H</sub>

- ◇ 特殊功能寄存器 SFR

- 128 个特殊寄存器

- 地址范围 FF80H~FFFFH

- ◇ 支持2种寻址方式

- 直接寻址

- 间接寻址

## 3. 3. 2 数据区地址映射

图 3-3 数据区地址映射示意图

## 3. 3. 3 通用数据存储器

通用数据存储器被用于临时存放数据和控制信息,可以在程序控制下进行读写操作。本芯片通用数据存储器空间为 128 Bytes,地址范围为 0000<sub>H</sub>~007F<sub>H</sub>。通用数据存储器的内容在上电复位后是不确定的,未下电的其他复位后,将保存复位前的内容。

## 3.3.4 特殊功能寄存器

特殊功能寄存器用于芯片对外设操作的控制设定。本芯片支持 128 个特殊寄存器,地址范围 FF80<sub>H</sub>~FFFF<sub>H</sub>。大多数寄存器都是可以读写的,仅有少数部分寄存器不对外开放。相关功能所使用的寄存器将分别在各个章节中描述。

V1.4 22/95

| FF80 <sub>H</sub> | IAD             | FFA0 <sub>H</sub> | INTG   | FFC0 <sub>H</sub> | RXB     |  |  |  |  |

|-------------------|-----------------|-------------------|--------|-------------------|---------|--|--|--|--|

| FF81 <sub>H</sub> | IAAL            | FFA1 <sub>H</sub> | LVD0C  | FFC1 <sub>H</sub> | RXC     |  |  |  |  |

| FF82 <sub>H</sub> | IAAH            | FFA2 <sub>H</sub> | LVD1C  | FFC2 <sub>H</sub> | TXB     |  |  |  |  |

| FF83 <sub>H</sub> | _               | FFA3 <sub>H</sub> | INTF1  | FFC3 <sub>H</sub> | TXC     |  |  |  |  |

| FF84 <sub>H</sub> | PSW             | FFA4 <sub>H</sub> | INTE1  | FFC4 <sub>H</sub> | BRR     |  |  |  |  |

| FF85 <sub>H</sub> | AREG            | FFA5 <sub>H</sub> | OSCCAL | FFC5 <sub>H</sub> | _       |  |  |  |  |

| FF86 <sub>H</sub> | _               | FFA6 <sub>H</sub> | WDTCAL | FFC6 <sub>H</sub> | _       |  |  |  |  |

| FF87 <sub>H</sub> | FRAL            | FFA7 <sub>H</sub> | PWRC   | FFC7 <sub>H</sub> | _       |  |  |  |  |

| FF88 <sub>H</sub> | FRAH            | FFA8 <sub>H</sub> | OSCC   | FFC8 <sub>H</sub> | _       |  |  |  |  |

| FF89 <sub>H</sub> | ROMDL           | FFA9 <sub>H</sub> | WKDC   | FFC9 <sub>H</sub> | CALPROT |  |  |  |  |

| FF8A <sub>H</sub> | ROMDH           | $FFAA_H$          | OSCP   | FFCA <sub>H</sub> | _       |  |  |  |  |

| FF8B <sub>H</sub> | PCRL            | $FFAB_H$          | WDTC   | FFCB <sub>H</sub> | _       |  |  |  |  |

| FF8C <sub>H</sub> | PCRH            | $FFAC_H$          | PWEN   | FFCC <sub>H</sub> | _       |  |  |  |  |

| FF8D <sub>H</sub> | _               | $FFAD_H$          | _      | FFCD <sub>H</sub> | _       |  |  |  |  |

| FF8E <sub>H</sub> | PA              | $FFAE_H$          | _      | FFCE <sub>H</sub> | _       |  |  |  |  |

| FF8F <sub>H</sub> | PAT             | $FFAF_H$          | _      | FFCF <sub>H</sub> | _       |  |  |  |  |

| FF90 <sub>H</sub> | PB              | FFB0 <sub>H</sub> | T8N    | FFD0 <sub>H</sub> | _       |  |  |  |  |

| FF91 <sub>H</sub> | PBT             | FFB1 <sub>H</sub> | T8NC   | FFD1 <sub>H</sub> | _       |  |  |  |  |

| FF92 <sub>H</sub> |                 | FFB2 <sub>H</sub> | T8P1   | FFD2 <sub>H</sub> | _       |  |  |  |  |

| FF93 <sub>H</sub> | _               | FFB3 <sub>H</sub> | T8P1C  | FFD3 <sub>H</sub> | _       |  |  |  |  |

| FF94 <sub>H</sub> | N_PAD           | FFB4 <sub>H</sub> | T8P1P  | FFD4 <sub>H</sub> | _       |  |  |  |  |

| FF95 <sub>H</sub> | N_PBD           | FFB5 <sub>H</sub> | T8P1RL | FFD5 <sub>H</sub> | _       |  |  |  |  |

| FF96 <sub>H</sub> | N_PAU           | FFB6 <sub>H</sub> | T8P1RH |                   |         |  |  |  |  |

| FF97 <sub>H</sub> | N_PBU           | FFB7 <sub>H</sub> | T8P1OC |                   |         |  |  |  |  |

| FF98 <sub>H</sub> |                 | FFB8 <sub>H</sub> | T8P2   | FFF8 <sub>H</sub> | _       |  |  |  |  |

| FF99 <sub>H</sub> |                 | FFB9 <sub>H</sub> | T8P2C  | FFF9 <sub>H</sub> | _       |  |  |  |  |

| FF9A <sub>H</sub> |                 | $FFBA_H$          | T8P2P  | $FFFA_H$          | _       |  |  |  |  |

| FF9B <sub>H</sub> |                 | FFBB <sub>H</sub> | T8P2RL | $FFFB_H$          | _       |  |  |  |  |

| FF9C <sub>H</sub> |                 | FFBC <sub>H</sub> | T8P2RH | FFFC <sub>H</sub> | _       |  |  |  |  |

| FF9D <sub>H</sub> | INTF0           | $FFBD_H$          | T8P2OC | $FFFD_H$          | _       |  |  |  |  |

| FF9E <sub>H</sub> | INTE0           | $FFBE_H$          | PWM1C  | FFFE <sub>H</sub> | _       |  |  |  |  |

| FF9F <sub>H</sub> | INTC0           | $FFBF_H$          | PWM2C  | FFFF <sub>H</sub> | _       |  |  |  |  |

| 注: "-             | 注: "—"为保留空间,未使用 |                   |        |                   |         |  |  |  |  |

图 3-4 特殊功能寄存器空间

## 3.3.5 寻址方式

SRAM 数据存储器的寻址方式支持直接寻址和间接寻址。

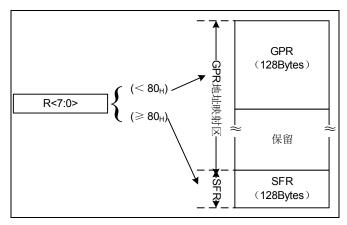

## 3. 3. 5. 1 直接寻址

在直接寻址时,指令中的 8 位地址信息用于 GPR 和 SFR 寻址。当指令中的 8 位地址信息 R<7:0>小于  $80_H$ 时,直接寻址 GPR 映射区。当 R<7:0>大于或等于  $80_H$ 时,直接寻址 SFR 映射区。

图 3-5 普通直接寻址示意图

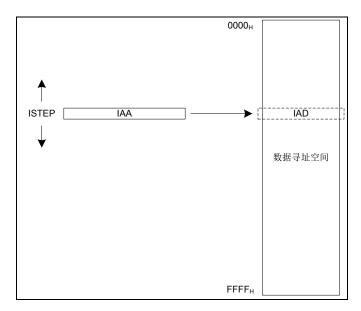

#### 3. 3. 5. 2 间接寻址

间接寻址是通过 16 位间接地址寄存器 IAA(由 2 个 8 位寄存器 IAAH 和 IAAL 组成)和 8 位虚拟数据寄存器 IAD 间接访问数据寻址空间中的存储单元,寻址空间为 0000<sub>H</sub>~ FFFF<sub>H</sub>。先将访问目的地址存放于间接地址寄存器 IAA,再通过指令对 IAD 进行读/写操作,实际的读/写操作对象则是 IAA 指向的数据寻址空间中的目的地址单元。

由于 IAD 寄存器本身也映射到数据寻址空间的 FF80<sub>H</sub> 地址,因此,当 IAA 存放的地址值为 FF80<sub>H</sub>时,读/写 IAD 相当于用间接寻址方式访问虚拟寄存器 IAD 本身,此时读操作将始终读出为  $00_H$ ,写操作则是一个空操作(可能影响状态位)。

ISTEP 指令,用来对 16 位间接地址寄存器 IAA 进行偏移操作。执行该指令时,先将指令字中的 8 位有符号立即数进行符号位扩展为 16 位数,再将 IAA 的值加上这个数的结果存回 IAA 寄存器。ISTEP 可实现的偏移范围为-128~127。虽然只有 8 位立即数,但是该条指令对整个 IAA(IAAL 和 IAAH)进行 16 位计算。计算的结果依然存放于 IAAL 和 IAAH中。

图 3-6 间接寻址示意图

## 应用例程:采用间接寻址将(020<sub>H</sub>~02F<sub>H</sub>)的寄存器清零。

CLR IAAH

MOVI 0X20 ; 对指针初始化 MOVA IAAL ;IAA 指向 RAM

NEXT1:

CLR IAD ;清零IAD寄存器 ISTEP0X01 ; 指针 IAA 内容加 1

JBS IAAL, 4

GOTONEXT1 ; 未完成,循环到下一个单元清零

CONTINUE:

; 已经完成,继续执行后面的程序 . . . . . .

## 3. 3. 6 特殊功能寄存器

| IAD: 间 | IAD: 间接寻址数据寄存器 |          |     |     |     |     |     |     |  |  |  |

|--------|----------------|----------|-----|-----|-----|-----|-----|-----|--|--|--|

| Bit    | 7              | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

| Name   |                | IAD<7:0> |     |     |     |     |     |     |  |  |  |

| R/W    | R/W            | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| POR    | 0              | 0        | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

Bit 7~0 IAD<7:0>: 间接寻址数据

| IAAL: 间接寻址索引寄存器低 8 位 |     |          |     |     |     |     |     |     |  |  |

|----------------------|-----|----------|-----|-----|-----|-----|-----|-----|--|--|

| Bit                  | 7   | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name                 |     | IAA<7:0> |     |     |     |     |     |     |  |  |

| R/W                  | R/W | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR                  | 0   | 0        | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

Bit 7~0 IAA<7:0>: 间接寻址索引低 8 位

| IAAH: | 间接寻址索引寄存器高8位 |                 |     |     |     |     |     |     |  |  |

|-------|--------------|-----------------|-----|-----|-----|-----|-----|-----|--|--|

| Bit   | 7            | 7 6 5 4 3 2 1 0 |     |     |     |     |     |     |  |  |

| Name  |              | IAA<15:8>       |     |     |     |     |     |     |  |  |

| R/W   | R/W          | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR   | 0            | 0               | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

Bit 7~0 IAA<15:8>: 间接寻址索引高 8 位

## 3.4 EEPROM存储器

## 3.4.1 概述

- ◇ 2线串行接口,完全兼容 I2C 总线传输协议

- ◇ I2C 时钟频率: 150KHz (VDD=3.0V~5.0V)

- ◇ 可按字节写

- ◇ 可按页写(8 Bytes/页)

- ◇ 内部写周期(最大 5ms)

- ◇ 自动递增地址

- ◇ 可按字节随机读和序列读

- ◇ 擦写寿命: 100 万次

## 3.4.2 详细操作说明

## 数据传输

内部 EEPROM 存储器与内部 MCU 的通信遵循 I2C 总线传输协议,总线上发送数据的器件为内部 MCU (主器件),接收数据的器件为内部 EEPROM (从器件),只有当总线处于空闲状态时才可以启动数据传输,每次数据传输均开始于 START 条件,结束于 STOP 条件,信息以字节为单位传输,第 9 位由内部 EEPROM 产生应答。

## 起始条件与停止条件

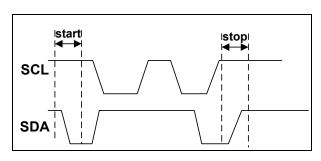

数据与时钟都为高则为总线处于空闲状态,当 SCL 为高电平时,SDA 的下降沿为起始条件,SDA 的上升沿为停止条件。见下图:

图 3-7 起始与停止条件时序图

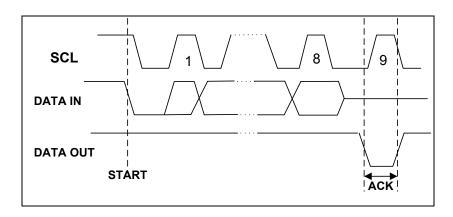

#### 应答

总线上的从器件每接收到一个字节就产生一个应答信号即低电平信号,因此主器件必须产生一个额外的时钟脉冲,即第9个脉冲。见下图:

图 3-8 应答时序图

## 存储器复位

当协议产生中断、掉电或系统复位后, I2C 总线可以通过以下步骤复位:

- (1) 产生 9 个时钟周期。

- (2) 时钟线 SCL 与 SDA 数据线同时为高。

- (3) 产生一个起始条件。

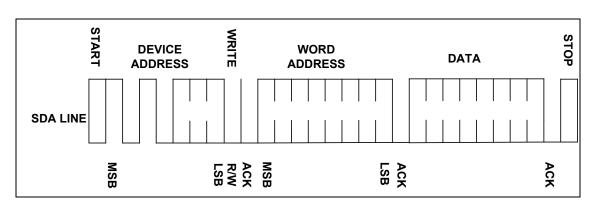

#### 字节写操作

字节写操作在主器件接收到从器件地址和 ACK 应答后,接收 8 位的字地址,接收到这个地址后内部 EEPROM 应答"0",然后是主器件发送一个 8 位数据,在接收完 8 位数据后,从器件应答"0",最后必须由主器件发送停止条件来终止写序列。此时从器件进入内部写周期 t<sub>WR</sub> 数据写入到非易失存储器中,此期间所有输入都无效,直到写周期完成,内部 EEPROM 才会有应答。见下图:

图 3-9 字节写时序图

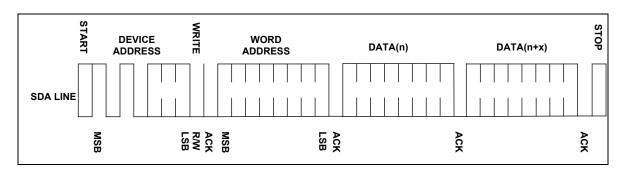

#### 页写操作

从器件内部 EEPROM 按每页 8 字节执行页写,页写初始化与字节写相同,只是主器件不会在第一个数据后发送停止条件,而是在内部 EEPROM 的应答后接着发送 7 个数据,从器件 EEPROM 接收到每个数据后都应答"0",最后仍然由主器件发送停止条件,终止写序列。

接收到每个数据后,字地址的低 3 位内部自动加 1,高位地址不变,维持在当前页内。当内部产生的字地址达到该页边界地址时,随后的数据写入该页的页首,如果超过 8 个数据传送给了从器件内部 EEPROM,字节地址将回到该页的首字节,先前的字节被覆盖。见下图:

V1.4 27/95

图 3-10 页写时序图

## 应答查询

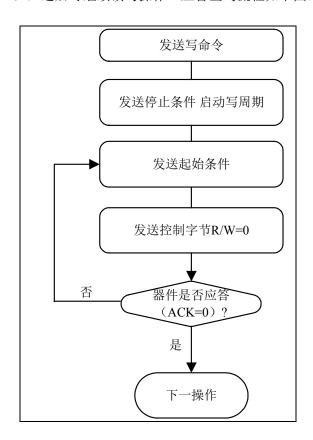

一旦内部写周期启动,从器件输入无效,此时可启动应答查询。只有内部写周期完成,从器件才会应答"0",之后可继续读写操作。应答查询流程如下图:

图 3-11 应答查询流程图

#### 读操作

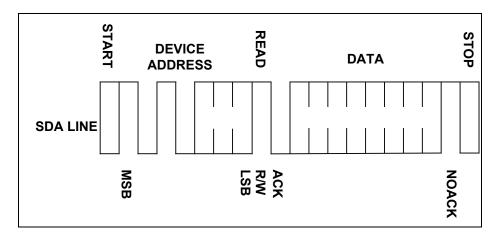

读操作与写操作初始化相同,只是器件地址中的读写选择位为"1",读操作有三种方式: 当前地址读、随机读、顺序读。

#### 1) 当前地址读

内部地址计数器保存着上次访问时最后一个地址加 1 的值。只要芯片有电,该地址一直保存,当读到最后页的最后地址,地址会回转到 0,当写到某页尾的最后一个字节,地址会回到该页的首字节。接收器件地址(读写选择位为"1")、EEPROM 应答 ACK 后,当前地址的数据就随时钟送出。主器件无需应答"0",但需要发送停止条件。见下图:

V1.4 28/95

图 3-12 当前地址读时序图

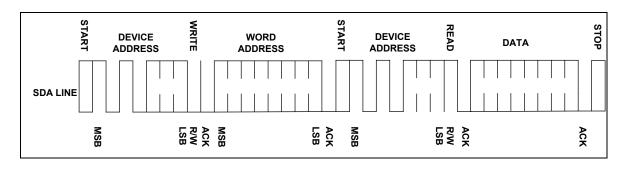

#### 2) 随机读

随机读需先写一个目标字地址,一旦从器件接收了器件地址和字地址并应答了 ACK 后,主器件就产生一个重复的起始条件。主器件发送器件地址(读/写选择位为"1"),从器件 应答 ACK 后,并随时钟送出数据。主器件无需应答"0",但需发送停止条件。见下图:

图 3-13 随机读时序图

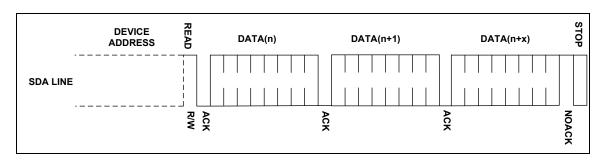

#### 3) 顺序读

顺序读可通过"当前地址读"或"随机读"启动。主器件接收到一个数据后,应答 ACK,只要 EEPROM 接收到 ACK,将自动增加字地址并继续随时钟发出后面的数据,若达到存储器地址末尾时,地址自动回转到 0,仍可继续随机读取数据。主器件不应答"0",而发送停止条件,即可结束顺序读操作。见下图:

图 3-14 顺序读时序图

V1.4 29/95

## 第4章 输入/输出端口

## 4.1 概述

输入/输出端口是芯片的最基本组成部分,本芯片最多支持 7 个 I/O 端口和 1 个输入端口。除PA1 为 TTL/SMT 输入外,其它所有 I/O 端口都是 TTL/SMT 输入和 CMOS 输出驱动。

- ◇ PA 输入/输出端口功能组件

- 3 位双向输入/输出和 1 位输入端口

- TTL/SMT 输入和 CMOS 输出驱动

- 端口输入/输出控制寄存器(PAT)

- 端口弱上拉控制寄存器(N PAU)

- 端口弱下拉控制寄存器(N\_PAD)

- PA0~3 支持外部按键中断功能

- ◇ PB 输入/输出端口功能组件

- 4 位双向输入/输出端口

- TTL/SMT 输入和 CMOS 输出驱动

- 端口输入/输出控制寄存器 (PBT)

- 端口弱上拉控制寄存器(N PBU)

- 端口弱下拉控制寄存器(N PBD)

- PB0 支持外部端口中断功能

- PB1 支持外部按键中断功能

- 注 1: 当端口设置为输出、外部振荡器时钟端口时,内部弱上/下拉自动禁止。

- 注 2: PB2/PB3 内部与 EEPROM SCL/SDA 相连,本芯片中未引出。

## 4.2 结构框图

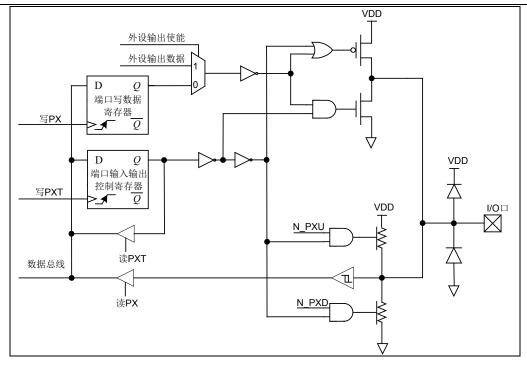

图 4-1 输入/输出端口结构图——PA0/PA2/PA3/PBx

V1.4 30/95

图 4-2 输入端口结构图——PA1

注: PA1 端口对应的 PAT 控制位始终为 1,即 PA1 只能作输入用。

## 4.3 I/O端口功能设置

## 4.3.1 I/O端口输入/输出控制

芯片中除 PA1 外的其他 I/O 端口都具有输入/输出的能力,端口控制寄存器 PxT 用于相应端口的输入或输出功能选择。当 I/O 端口设置为数字输出状态时,I/O 端口输出 Px 寄存器内容,即相应 I/O 端口电平状态,读取 Px 寄存器的操作实际为读取相应 I/O 端口电平状态。当 I/O 端口设置为数字输入状态时,读取 Px 寄存器的操作实际为读取相应 I/O 端口电平状态。

## 4.3.2 I/O端口弱上拉、弱下拉功能

很多产品的应用中需要端口连接上拉或下拉电阻,使端口固定在一个稳定的电平状态,防止外界干扰以及其它影响。本芯片中只有 PA1 端口默认弱上拉使能,其它所有端口均提供独立的弱上、下拉功能,可通过软件独立配置。

| 管脚 | 0  | 1  | 2  | 3  | 4 | 5 | 6 | 7 |

|----|----|----|----|----|---|---|---|---|

| PA | 支持 | 支持 | 支持 | 支持 | - | - | - | - |

| PB | 支持 | 支持 | 支持 | 支持 | - | - | - | - |

表 4-1 I/O 端口弱上拉

| 管脚 | 0  | 1   | 2  | 3  | 4 | 5 | 6 | 7 |

|----|----|-----|----|----|---|---|---|---|

| PA | 支持 | 不支持 | 支持 | 支持 | - | - | - | - |

| PB | 支持 | 支持  | 支持 | 支持 | - | - | - | - |

表 4-2 I/O端口弱下拉

## 4.3.3 I/O端口复用功能

为了使资源合理利用最优化,本芯片大部分的 I/O 端口都具有复用功能。当端口用于复用功能时,管脚电平由复用功能决定。

V1.4 31/95

## 4.4 端口中断

#### 4.4.1 按键中断(KINT)

本芯片外部端口支持 1 组外部按键中断。按键中断支持最多 5 个按键输入端 KIN<4:0>, 5 个按键共用一个按键中断使能位 KIE(INTEO<0>)及按键中断标志位 KIF(INTFO<0>),每个输入端可以由相应的按键屏蔽位 KMSKx(INTCO<4:0>)屏蔽,任何其中一个按键中断产生将影响中断标志 KIF。

端口电平变化可以产生中断,在按键中断使能(KMSKn=1, KIE=1)的情况下,输入端口与锁存器上的最后输入值进行比较,如果不匹配引起中断,中断标志位置 1, 此中断能将芯片从睡眠状态唤醒。

用户可在中断服务程序中用软件清除该中断标志,操作步骤如下:

- 1) 对端口寄存器进行读或者写操作,结束端口电平与锁存器值的不匹配条件;

- 2) 软件清除中断标志位。

在按键中断使能(KMSKn=1, KIE=1)前,先对端口寄存器进行读或者写的操作,清除中断标志位,以免误产生中断。

| 管脚名 | 端口输入 | 按键屏蔽  | 中断使能 | 中断标志 |

|-----|------|-------|------|------|

| PA0 | KIN0 | KMSK0 |      |      |

| PA1 | KIN1 | KMSK1 |      |      |

| PA2 | KIN2 | KMSK2 | KIE  | KIF  |

| PA3 | KIN3 | KMSK3 |      |      |

| PB1 | KIN4 | KMSK4 |      |      |

表 4-3 按键中断

## 4. 4. 2 外部端口中断 (PINT)

本芯片外部端口支持一个外部端口中断。端口中断只支持 1 个输入端 PINTO,外部端口中断由相应的 PIE(INTEO<2>)使能,通过 PEGO(INTCO<5>)选择上升沿触发还是下降沿触发。当外部中断已配置,且输入信号变化满足触发条件时,将产生 PINT 外部端口中断,中断产生将影响相应的中断标志 PIF(INTFO<2>)。此中断能将芯片从睡眠状态唤醒。

| 管朋 | 却名 | 端口输入  | 边沿选择 | 中断名  | 中断使能 | 中断标志 |

|----|----|-------|------|------|------|------|

| PI | В0 | PINT0 | PEG0 | PINT | PIE  | PIF  |

表 4-4 外部端口中断

## 4.5 I/O端口操作注意事项

当执行以端口寄存器为目标的操作时,芯片实际执行读-修改-写过程,即先读取该组全部 I/O 端口的电平,修改后再写回端口寄存器。位操作指令对 I/O 的修改操作只影响选定的位,不会影响同组其它 I/O 端口。因此建议用户对单个 I/O 的修改采用位操作指令。此外用户在对 I/O 端口的复用功能使能和关闭时,应充分考虑当前 I/O 端口的输出寄存器值,并判断是否需要重新对这些 I/O 端口进行初始化赋值。

V1.4 32/95

## 4.6 特殊功能寄存器

输入/输出端口的设置包括一系列的寄存器控制,PX 寄存器用于显示 PX 端口的电平状态,PXT 寄存器用于设置 PX 端口的输入输出状态,N\_PXU / N\_PXD 用于设置 PX 端口的弱上拉 / 弱下拉电阻的连接状况。

| PA: PA | PA: PA 端口电平状态寄存器 |   |   |   |     |     |     |     |  |  |  |  |

|--------|------------------|---|---|---|-----|-----|-----|-----|--|--|--|--|

| Bit    | 7                | 6 | 5 | 4 | 3   | 2   | 1   | 0   |  |  |  |  |

| Name   | _                | _ | _ | _ | PA3 | PA2 | PA1 | PA0 |  |  |  |  |

| R/W    | _                | _ | _ | _ | R/W | R/W | R/W | R/W |  |  |  |  |

| POR    | 0                | 0 | 0 | 0 | Х   | Х   | х   | Х   |  |  |  |  |

"x": 未知

Bit 7~4 未使用

Bit 3~0 PA<3:0>: PA 端口电平状态

0: 低电平1: 高电平

| PAT: PA           | PAT: PA 端口输入输出控制寄存器 |   |   |   |      |      |      |      |  |  |  |  |

|-------------------|---------------------|---|---|---|------|------|------|------|--|--|--|--|

| Bit 7 6 5 4 3 2 1 |                     |   |   |   |      |      |      |      |  |  |  |  |

| Name              | _                   | _ | _ | _ | PAT3 | PAT2 | PAT1 | PAT0 |  |  |  |  |

| R/W               | _                   | _ | _ | _ | R/W  | R/W  | R    | R/W  |  |  |  |  |

| POR               | 0                   | 0 | 0 | 0 | 1    | 1    | 1    | 1    |  |  |  |  |

Bit 7~4 未使用

Bit 3 PAT3: PA3 端口输入输出状态选择位(复用为外部振荡端口时,硬件固定为输入状态)

0:输出状态1:输入状态

Bit 2 PAT2: PA2 端口输入输出状态选择位(复用为外部振荡端口时,硬件固定为输入状态)

0:输出状态1:输入状态

Bit 1 PAT1: 硬件固定为 1,该端口只能用作输入

Bit 0 PATO: PAO 端口输入输出状态选择位

0: 输出状态1: 输入状态

| PB: PB | PB: PB 端口电平状态寄存器 |   |   |   |     |     |     |     |  |  |  |  |

|--------|------------------|---|---|---|-----|-----|-----|-----|--|--|--|--|

| Bit    | 7                | 6 | 5 | 4 | 3   | 2   | 1   | 0   |  |  |  |  |

| Name   | _                | _ | _ | _ | PB3 | PB2 | PB1 | PB0 |  |  |  |  |

| R/W    | _                | _ | _ | _ | R/W | R/W | R/W | R/W |  |  |  |  |

| POR    | 0                | 0 | 0 | 0 | Х   | Х   | х   | Х   |  |  |  |  |

"x": 未知

Bit 7~4 未使用

Bit 3~0 PB<3:0>: PB 端口电平状态

V1.4 33/95

0: 低电平

1: 高电平

| PBT: PE             | 3 端口输入轴 | PBT: PB 端口输入输出控制寄存器 |   |   |      |      |      |      |  |  |  |  |  |

|---------------------|---------|---------------------|---|---|------|------|------|------|--|--|--|--|--|

| Bit 7 6 5 4 3 2 1 0 |         |                     |   |   |      |      |      |      |  |  |  |  |  |

| Name                | _       | _                   | _ | _ | PBT3 | PBT2 | PBT1 | PBT0 |  |  |  |  |  |

| R/W                 | _       | _                   | _ | _ | R/W  | R/W  | R/W  | R/W  |  |  |  |  |  |

| POR                 | 0       | 0                   | 0 | 0 | 1    | 1    | 1    | 1    |  |  |  |  |  |

Bit 7~4 未使用

Bit 3~0 PBT<3:0>: PB 端口输入输出状态选择位

0:输出状态1:输入状态

| N_PAU:            | N_PAU: PA 端口弱上拉控制寄存器 |   |   |   |        |        |        |        |  |  |  |  |

|-------------------|----------------------|---|---|---|--------|--------|--------|--------|--|--|--|--|

| Bit 7 6 5 4 3 2 1 |                      |   |   |   |        |        |        | 0      |  |  |  |  |

| Name              | _                    | _ | _ | _ | N_PAU3 | N_PAU2 | N_PAU1 | N_PAU0 |  |  |  |  |

| R/W               | _                    |   |   |   | R/W    | R/W    | R/W    | R/W    |  |  |  |  |

| POR               | 0                    | 0 | 0 | 0 | 1      | 1      | 0      | 1      |  |  |  |  |

Bit 7~4 未使用

Bit 3~0 N\_PAU <3:0>: PA 端口内部弱上拉控制位

0: 使能 1: 禁能

| N_PBU: | N_PBU: PB 端口弱上拉控制寄存器 |   |   |   |        |        |        |        |  |  |  |  |

|--------|----------------------|---|---|---|--------|--------|--------|--------|--|--|--|--|

| Bit    | 7                    | 6 | 5 | 4 | 3      | 2      | 1      | 0      |  |  |  |  |

| Name   | _                    | _ | _ | _ | N_PBU3 | N_PBU2 | N_PBU1 | N_PBU0 |  |  |  |  |

| R/W    | _                    | _ | _ | _ | R/W    | R/W    | R/W    | R/W    |  |  |  |  |

| POR    | 0                    | 0 | 0 | 0 | 1      | 1      | 1      | 1      |  |  |  |  |

Bit 7~4 未使用

Bit 3~0 N\_PBU <3:0>: PB 端口内部弱上拉控制位

0: 使能 1: 禁能

| N_PAD: | N_PAD: PA 端口弱下拉控制寄存器 |   |   |   |        |        |   |        |  |  |  |  |

|--------|----------------------|---|---|---|--------|--------|---|--------|--|--|--|--|

| Bit    | 7                    | 6 | 5 | 4 | 3      | 2      | 1 | 0      |  |  |  |  |

| Name   | _                    | _ | _ | _ | N_PAD3 | N_PAD2 | _ | N_PAD0 |  |  |  |  |

| R/W    | _                    | _ | _ |   | R/W    | R/W    | _ | R/W    |  |  |  |  |

| POR    | 0                    | 0 | 0 | 0 | 1      | 1      | 1 | 1      |  |  |  |  |

Bit 7~4,1 未使用

Bit 3~2,0 N\_PAD <3:2,0>: PA 端口内部弱下拉控制位

0: 使能 1: 禁能

| N_PBD: | N_PBD: PB 端口弱下拉控制寄存器 |   |   |   |        |        |        |        |  |  |  |  |

|--------|----------------------|---|---|---|--------|--------|--------|--------|--|--|--|--|

| Bit    | 7                    | 6 | 5 | 4 | 3      | 2      | 1      | 0      |  |  |  |  |

| Name   | _                    |   |   | _ | N_PBD3 | N_PBD2 | N_PBD1 | N_PBD0 |  |  |  |  |

| R/W    | _                    | _ |   |   | R/W    | R/W    | R/W    | R/W    |  |  |  |  |

| POR    | 0                    | 0 | 0 | 0 | 1      | 1      | 1      | 1      |  |  |  |  |

Bit 7~4 未使用

Bit 3~0 N\_PBD <3:0>: PB 端口内部弱下拉控制位

0: 使能1: 禁能

## 第5章 特殊功能及操作特性

## 5.1 系统时钟与振荡器

## 5.1.1 概述

芯片运行所需要的时钟源由振荡器提供,不同的振荡器选择可以让使用者在不同的应用需求中实现更大范围的功能。本款芯片所提供的振荡器有三种:外部晶体/陶瓷振荡器 XTAL、内部高速 RC 振荡器(16MHz)和内部低速 RC 振荡器(32KHz)。灵活选择振荡器,使得产品在速度和功耗方面可以达到最优化。内部低速 RC 振荡器除了作为系统时钟源外,还可以为看门狗定时器等提供所需要的时钟源。

- ◇ 振荡器模式

- 外部振荡器 (HS/XT/LP)

- 内部 16MHz RC 振荡器 (可配置为 INTOSC 和 INTOSCIO)

- 内部 32KHz RC 振荡器

- ◇ 内部 16MHz RC 振荡器

- 8 位校准寄存器 (OSCCAL)

- 出厂前,在常温下已经校准在±2%以内

- 支持多种分频时钟

- ◇ 内部 32KHz RC 振荡器

- 8 位校准寄存器 (WDTCAL)

- ◇ 系统时钟切换

- 高速 HS/XT/INTOSCH 16MHz 振荡时钟与内部低速 INTOSCL 32KHz 时钟切换

- 外部低速 LP 振荡时钟与内部高速 INTOSCH 16MHz 时钟切换

- ◇ 振荡和暂停

- 在 IDLEO 模式下,振荡器暂停振荡

- 在 IDLE1 模式下,振荡器保持振荡,系统时钟暂停

## 5.1.2 时钟源

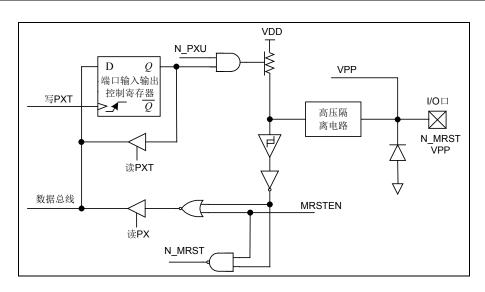

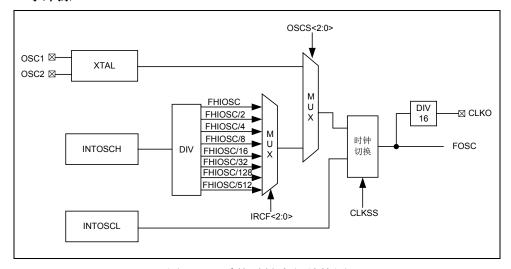

图 5-1 系统时钟内部结构图

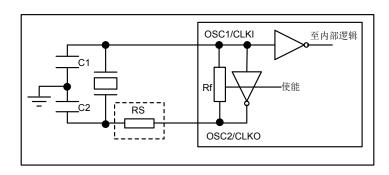

#### 5. 1. 2. 1 外部时钟

外部时钟包括晶体/陶瓷振荡器模式 (HS/XT/LP)。对于晶体/陶瓷振荡器而言,只要简单 地将晶体连接至 OSC1 和 OSC2 管脚间,就会产生振荡所需的相移及反馈。为保证振荡 频率更精准,需连接两个小容量电容 C1 和 C2 到 VSS,具体数值与所使用的晶体/陶瓷振荡器有关,电容参考取值范围为 15~33pF。根据所选择的振荡器频率,可分为三种模式: HS 模式、XT 模式和 LP 模式。当芯片配置字 OSCS<2:0> = 000 时,选择 LP 模式; 当 OSCS<2:0> = 010 时,选择 HS 模式; 当芯片配置字 OSCS<2:0> = 100 时,选择 XT 模式。芯片配置字 OSCS<2:0> = 100 时,选择 XT 模式。芯片配置字 OSCS<2:0> = 100 时,选择 XT

#### ◇ 晶体/陶瓷振荡器模式(HS、XT、LP模式)

HS/XT 晶振起振稳定时间为 512 个系统时钟。LP 晶振设计为低功耗振荡,LP 起振稳定时间和外部晶体结构有关系,通常在一秒左右。

图 5-2 晶体/陶瓷振荡器模式(HS、XT、LP模式)

#### 注:RS 为可选配置。

| Osc Type | 晶振频率           | C1*  | C2*       |  |

|----------|----------------|------|-----------|--|

| LP       | 32KHz          | 33pF | 33pF      |  |

| XT       | 1MHz           |      |           |  |

| ^1       | 4MHz 15 ~ 33pF |      | 15 ~ 33pF |  |

| 110      | 8MHz           |      |           |  |

| HS       | 16MHz          | 15pF | 15pF      |  |

表 5-1 晶体振荡器电容参数参考表

注\*: 此数据可根据晶振频率大小、外围电路的不同作微调。

#### 5. 1. 2. 2 内部高速 16MHz RC振荡器模式(INTOSCH)

芯片內置 16MHz RC 时钟振荡器,不需要外接其它外部器件。当配置字中的 OSCS<2:0>=000/110/111 且寄存器 OSCC 中的 CLKSS=1 时,选择内部 16MHz RC 作 为系统时钟源,此时 PA2 和 PA3 管脚复用为通用 I/O 端口。INTOSCH 16MHz 最低可分频至 32KHz,出厂前,内置 16MHz RC 时钟振荡器已在常温下校准。芯片上电时,会自动加载校准值,客户不需要对校准寄存器 OSCCAL 进行任何操作。

## 5. 1. 2. 3 内部低速 32kHz RC振荡器模式(INTOSCL)

芯片内置 32KHz RC 时钟振荡器,不需要外接其它外部器件,可用作 WDT 计数时钟源,也可配置为主系统时钟源。当配置字中的 OSCS<2:0>=010/100/110/111 且寄存器 OSCC

V1.4 37/95

中的 CLKSS=0 时,选择内部 32KHz RC 作为系统时钟源,此时 PA2 和 PA3 管脚复用为通用 I/O 端口。芯片上电时,会自动加载校准值,客户不需要对校准寄存器 WDTCAL 进行任何操作。

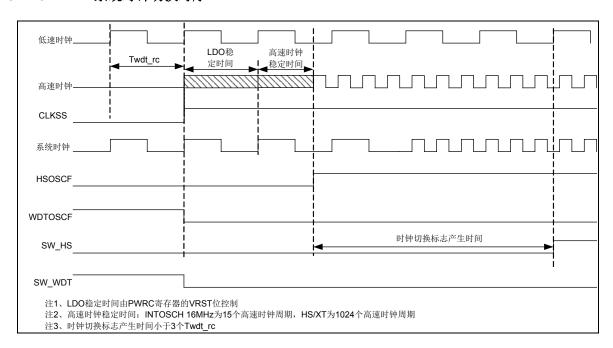

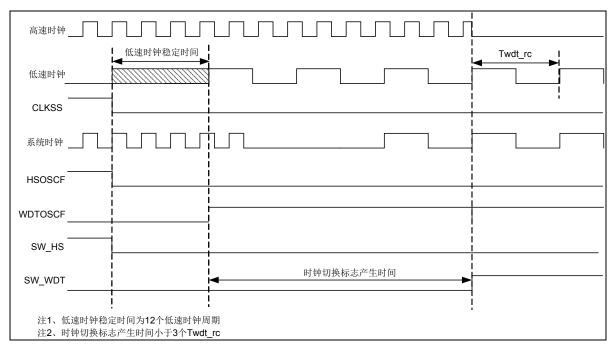

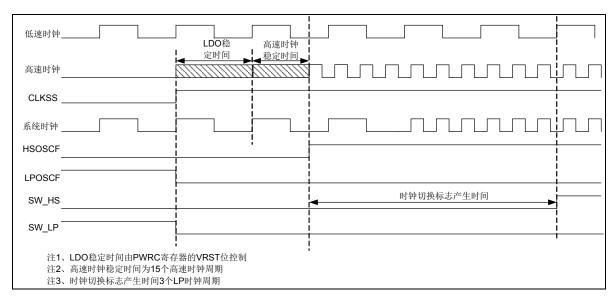

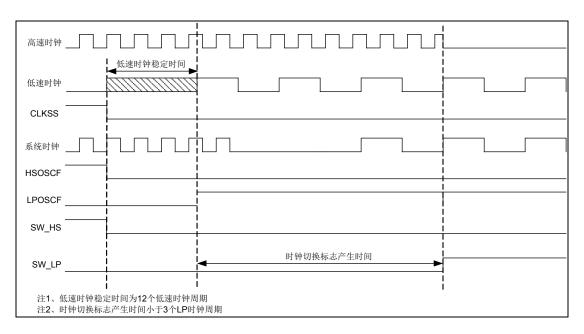

# 5. 1. 3 系统时钟切换

高频时钟能提供系统更高的性能,低频时钟能够提供更低的功耗。因此,根据用户需要, 灵活地安排高低频时钟切换,可以使系统在执行速度和功耗方面最优化。

系统可软件设置寄存器位 CLKSS (OSCC<7>),选择高、低速系统时钟。系统上电时,寄存器 CLKSS 的值默认为 0,工作在低速系统时钟模式下。

系统支持四种时钟切换:

- ◇ 内部低速 INTOSCL 32KHz 时钟切换到内部高速 INTOSCH/外部高速 HS/XT 时钟

- 设置芯片配置字 CFG\_WD 中的 OSCS<2:0>=010/100/110/111;

- 设置 OSCC 寄存器中的 CLKSS=1;

- 检测 OSCC 寄存器中的 HSOSCF 位, 直到检测到 HSOSCF=1;

- 等待一条 NOP 指令:

- 检测 PWEN 寄存器的 SW\_HS 位,直到检测到 SW\_HS=1。

- ◇ 内部高速 INTOSCH/外部高速 HS/XT 时钟切换到内部低速 INTOSCL 时钟

- 设置芯片配置字 CFG WD 中的 OSCS<2:0>=010/100/110/111;

- 设置 OSCC 寄存器中的 CLKSS=0;

- 检测 OSCC 寄存器中的 WDTOSCF 位, 直到检测到 WDTOSCF =1;

- 等待一条 NOP 指令;

- 检测 PWEN 寄存器的 SW WDT 位, 直到检测到 SW WDT =1。

- ◇ 外部低速 LP 时钟切换到 INTOSCH 时钟钟

- 设置芯片配置字 CFG WD 中的 OSCS<2:0>=000;

- 设置 OSCC 寄存器中的 CLKSS=1;

- 检测 OSCC 寄存器中的 HSOSCF 位, 直到检测到 HSOSCF=1;

- 等待一条 NOP 指令:

- 检测 PWEN 寄存器的 SW\_HS 位, 直到检测到 SW\_HS=1。

- ◇ 内部高速 INTOSCH 时钟切换到外部低速 LP 时钟

- 设置芯片配置字 CFG WD 中的 OSCS<2:0>=000;

- 设置 OSCC 寄存器中的 CLKSS=0:

- 检测 OSCC 寄存器中的 LPOSCF 位, 直到检测到 LPOSCF =1;

- 等待一条 NOP 指令;

- 检测 PWEN 寄存器的 SW\_LP 位, 直到检测到 SW\_LP =1。

| 系统时钟来源  | OSCS<2:0>位 | CLKSS 位 |

|---------|------------|---------|

| LP      | 000        | 0       |

| HS      | 010        | 1       |

| XT      | 100        | 1       |

| INTOSCH | 000        | 1       |

| INTOSCH | 110        | 1       |

V1.4 38/95

| 系统时钟来源  | OSCS<2:0>位 | CLKSS 位 |

|---------|------------|---------|

|         | 111        | 1       |

|         | 010        | 0       |

| INTOSCL | 100        | 0       |

| INTOSCL | 110        | 0       |

|         | 111        | 0       |

表 5-2 振荡模式切换选择

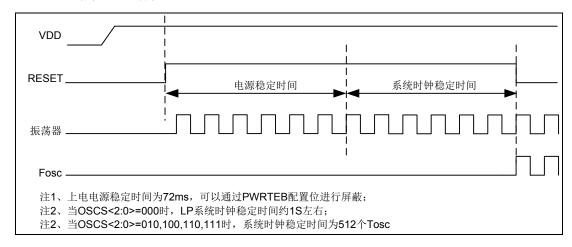

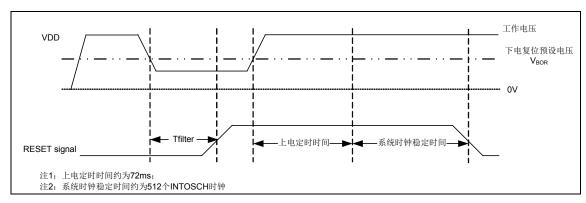

# 5. 1. 3. 1 系统上电时序

图 5-3 系统上电时序图

#### 5. 1. 3. 2 系统时钟切换时序

图 5-4 INTOSCL 时钟切换到 INTOSCH/HS/XT 时钟

图 5-5 INTOSCH/HS/XT 时钟切换到 INTOSCL 时钟

图 5-6 低速 LP 时钟切换到 INTOSCH 时钟

图 5-7 INTOSCH 时钟切换到低速 LP 时钟

# 5.1.4 系统时钟分频

当系统时钟来源于内部高频时钟 INTOSCH 16MHz 时,系统时钟支持 1 个最大分频比为 1:512 的分频器,最低可分频至 32KHz,可通过 OSSC 寄存器中的 IRCF<2:0>位进行选择分频比。

# 5.1.5 特殊功能寄存器

| CALPRO | CALPROT: 校准值保护寄存器 |   |   |   |   |   |   |         |  |  |  |

|--------|-------------------|---|---|---|---|---|---|---------|--|--|--|

| Bit    | 7                 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |  |  |  |

| Name   | _                 | _ | _ | _ | _ | _ | _ | CALPROT |  |  |  |

| R/W    | _                 | _ | _ | _ | _ | _ | _ | R/W     |  |  |  |

| POR    | 0                 | 0 | 0 | 0 | 0 | 0 | 0 | 1       |  |  |  |

Bit 7~1 未使用

Bit 0 CALPROT:校准值保护位

1: 校准值处于保护状态

0: 校准值处于去除保护状态

当 CALPROT 寄存器写入 55h 时,去除保护位,其他任何写入都是使能保护位。

注: CALPROT 保护的校准值寄存器为 OSCCAL, WDTCAL。

| OSCCAL | OSCCAL: 内部 16MHz 时钟校准寄存器 |     |     |     |     |     |     |     |  |  |

|--------|--------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| Bit    | 7                        | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

| Name   | OSCCAL<7:0>              |     |     |     |     |     |     |     |  |  |

| R/W    | R/W                      | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| POR    | 0                        | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

Bit 7~0 OSCCAL<7:0>: 内部 16MHz 时钟频率调节位

注:此寄存器受 CALPROT 寄存器保护。OSCCAL 寄存器主要是调整内部 16MHz 时钟的精度。在常温条件下,出厂时已经校准到 16MHz。如果没有特别需求,用户不需要设置此寄存器,以免覆盖芯片默认的时钟校准值。

V1.4 41/95

| oscc: | OSCC: 时钟控制寄存器 |           |     |     |   |         |        |        |  |  |

|-------|---------------|-----------|-----|-----|---|---------|--------|--------|--|--|

| Bit   | 7             | 6         | 5   | 4   | 3 | 2       | 1      | 0      |  |  |

| Name  | CLKSS         | IRCF<2:0> |     |     | _ | WDTOSCF | HSOSCF | LPOSCF |  |  |

| R/W   | R/W           | R/W       | R/W | R/W | _ | R       | R      | R      |  |  |

| POR   | 0             | 1         | 1   | 0   | 0 | 1       | 0      | 0      |  |  |

Bit 7 CLKSS: 低速时钟与高速时钟切换选择位

当 OSCS<2:0>=000 时:

0: 外部低速 LP 32KHZ 时钟源

1: 内部高速 INTOSCH 16MHz 时钟源

当 OSCS<2:0>=010/100/110/111 时:

0: 内部低速 INTOSCL 32KHZ 时钟源

1: 内部高速 INTOSCH 16MHz 或者外部高速 HS/XT 时钟源

Bit 6~4 IRCF<2:0>: 内部系统时钟频率选择位

000: 32KHZ

001: 125KHZ

010: 500KHz

011: 1MHz

100: 2MHz

101: 4MHz

110: 8MHz

111: 16MHz

Bit 3 未使用

Bit 2 WDTOSCF: 内部 32KHz 稳定标志位

0: 未稳定

1: 稳定

Bit 1 HSOSCF: 高速时钟稳定标志位

0: 未稳定

1: 稳定

Bit 0 LPOSCF:外部 LP 晶振稳定标志位

0: 未稳定

1: 稳定

| OSCP: 时钟控制写保护寄存器 |           |     |     |     |     |     |     |     |

|------------------|-----------|-----|-----|-----|-----|-----|-----|-----|

| Bit              | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Name             | OSCP<7:0> |     |     |     |     |     |     |     |

| R/W              | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR              | 1         | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

Bit 7~0 OSCP<7:0>: 时钟控制写保护位

OSCP 为 55<sub>H</sub>时,可以改变 IRCF 和 CLKSS 位。当 IRCF 和 CLKSS 被写时,OSCP

自动复位为 FF<sub>H</sub>。

OSCP不为55<sub>H</sub>时,对IRCF和CLKSS的写操作将被忽略。

| PWEN | PWEN: 功耗控制寄存器 |        |       |       |   |   |      |      |  |  |  |

|------|---------------|--------|-------|-------|---|---|------|------|--|--|--|

| Bit  | 7             | 6      | 5     | 4     | 3 | 2 | 1    | 0    |  |  |  |

| Name | _             | SW_WDT | SW_HS | SW_LP | _ | _ | RCEN | SREN |  |  |  |

| R/W  | _             | R      | R     | R     | _ | _ | R/W  | R/W  |  |  |  |

| POR  | 0             | 1      | 0     | 0     | 1 | 0 | 1    | 1    |  |  |  |

Bit 7,2 未使用

Bit 6 SW\_WDT: 切换到内部低速 32KHz 时钟标志位

0: 切换未完成1: 切换完成

Bit 5 SW\_HS: 切换到 HS/XT/INTOSCH 16MHz 高速时钟标志位

0: 切换未完成1: 切换完成

Bit 4 SW\_LP: 切换到外部低速 LP 晶振时钟标志位

0: 切换未完成1: 切换完成

Bit 3 未使用

Bit 1 RCEN: WDT 内部 RC 时钟使能位(软件设置 RCEN 为 1 使能)

当 CLKSS=1 时:

0: 关闭 WDT 内部 RC 时钟 1: 使能 WDT 内部 RC 时钟

当 CLKSS=0 时:

WDT 内部 RC 时钟一直使能,此位设置无效

Bit 0 SREN: 低电压检测复位软件使能位

需软件固定设置为1

注 1: 软件设置 RCEN 为 1 使能。

注 2: 如果需要频繁进行高、低速系统时钟切换,必须进行相应切换完成标志位 SW\_LP、SW\_HS 和 SW\_WDT 的 判断。

注 3: SREN 位需软件固定设置为 1, 否则会存在芯片系统复位异常的潜在风险。

# 5.2 看门狗定时器

## 5. 2. 1 概述

看门狗定时器是芯片的一个组成部分,它的功能在于在发生软件故障时,通过器件复位将芯片复位。若系统进入了错误的工作状态,看门狗可以在合理的时间范围内使芯片复位。使能看门狗时,若用户程序清除看门狗定时器失败,则在预定的时间范围内,看门狗会使系统复位。

#### ◇ WDT 定时器

- 8 位 WDT 定时计数器 (无实际物理地址,不可读写)

- 8 位预分频器 (无实际物理地址,不可读写)

- WDT 控制寄存器 (WDTC)

- 唤醒功能

- 复位功能

- ◇ 内部 WDT RC 振荡器

- 定时器时钟源为内部 32KHz RC 时钟

- 8 位 WDT 时钟校准寄存器 (WDTCAL)

- 出厂前,在常温下已经将频率校准在±15%以内,其高低温频偏对 WDT 计数溢出 周期的影响,见《电气特性》章节的描述

#### 5. 2. 2 内部结构图

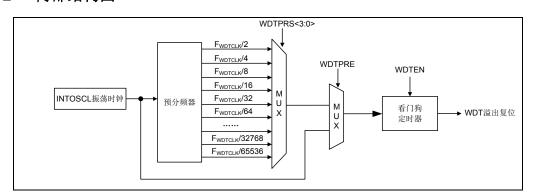

图 5-8 看门狗定时器内部结构图

## 5. 2. 3 WDT定时器

芯片提供 8 位 WDT 定时计数器,通过芯片配置字 WDTEN 可使能硬件看门狗 WDT。当芯片配置字 WDTEN 使能时,WDT 定时器计数使能;当 WDTEN 关闭时,WDT 定时器计数禁止。客户通过编程界面选择。

在 IDLE 模式下, WDT 计数溢出会唤醒 CPU;此外,WDT 计数溢出会复位芯片。为了避免不必要的复位,可使用 CWDT 指令适时清零 WDT 计数器。

WDT 支持一个预分频器,可通过 WDTC 寄存器中的 WDTPRS<3:0>位设置 WDT 时钟源的预分频比,再将分频后的时钟信号作为 WDT 定时器的计数时钟。WDT 时钟源来自内部32KHz RC 振荡器 INTOSCL 时钟。当 WDTPRE(WDTC<4>)清零,禁止预分频器,WDT 时钟为32KHz,常温下 WDT 的计数溢出时间约为8ms。当 WDTPRE(WDTC<4>)置 1,使能预分频器。

V1.4 44/95

注: WDT 定时器工作时, RCEN (PWEN<1>) 必须置 1。

# 5.2.4 特殊功能寄存器

WDT 的功能控制由 WDTC 寄存器和芯片配置字共同完成。WDT 功能的使能控制由芯片配置字控制,而 WDT 预分频器的使能控制以及 WDT 预分频器的分频比选择则由 WDTC 寄存器设置。此外,WDTCAL 寄存器用于内部 32KHz 时钟校准。

| WDTCAL | WDTCAL: 内部 32KHz 时钟校准寄存器 |     |     |     |     |     |     |     |  |

|--------|--------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| Bit    | 7                        | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

| Name   | WDTCAL<7:0>              |     |     |     |     |     |     |     |  |

| R/W    | R/W                      | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| POR    | 0                        | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

Bit 7~0 WDTCAL<7:0>: 内部 32KHz 时钟频率调节位

注:此寄存器受 CALPROT 寄存器保护。WDTCAL 寄存器主要是调整内部 32KHz 时钟的精度。在芯片出厂前,已经设置好校准值,禁止用户程序改写该寄存器,否则会导致芯片对应的功能模块工作异常。

| WDTC: | WDTC: WDT 控制寄存器 |   |   |        |             |     |     |     |  |  |

|-------|-----------------|---|---|--------|-------------|-----|-----|-----|--|--|

| Bit   | 7               | 6 | 5 | 4      | 3           | 2   | 1   | 0   |  |  |

| Name  | _               | _ | _ | WDTPRE | WDTPRS<3:0> |     |     |     |  |  |

| R/W   | _               | _ | _ | R/W    | R/W         | R/W | R/W | R/W |  |  |

| POR   | 0               | 0 | 0 | 1      | 0           | 1   | 1   | 1   |  |  |

Bit 7 未使用,需保留为 0

Bit 6~5 未使用

Bit 4 WDTPRE: WDT 预分频器使能位

0: 禁止 1: 使能

Bit 3~0 WDTPRS <3:0>: WDT 预分频器分频比选择位

0000: 1:2 0001: 1:4

0010: 1:8

0011: 1:16

0100: 1:32

0101: 1:64 0110: 1:128

0111: 1:256 (默认)

1000: 1:512

1001: 1:1024

1010: 1:2048

1011: 1:4096

1100: 1:8192

1101: 1:16384

1110: 1:32768

1111: 1:65536

# 5.3 复位模块

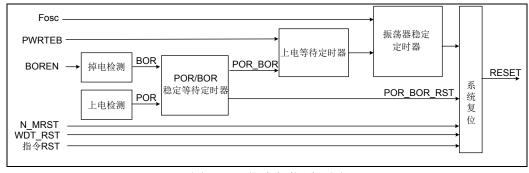

# 5.3.1 概述

复位功能是所有芯片中基本的部分,该芯片支持五种复位方式:

- ◇ 上电复位 POR

- ◇ 下电复位 BOR

- ◇ 外部端口 N\_MRST 复位,低电平复位有效

- ◇ 看门狗定时器 WDT 溢出复位

- ◇ 软件执行指令 RST 复位

图 5-9 芯片复位原理图

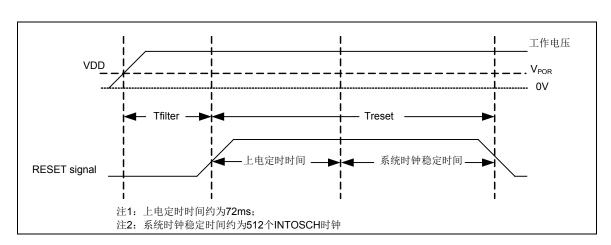

# 5.3.2 上电复位

芯片上电过程中会产生 POR 复位,并且该复位信号将会一直保持到电源电压升高到芯片能够正常工作的电压为止。系统上电过程呈逐渐上升的曲线形式,需要一定时间才能达到正常电平值。上电复位的时序如下:

图 5-10 上电复位时序示意图

# 5.3.3 下电复位

下电复位针对外部因素引起的系统电压跌落情形(例如:更换电池),下电复位可能会引起系统工作状态不正常或程序执行错误。

图 5-11 下电复位时序示意图

- 注 1: 72ms 等待稳定时间可以通过 PWRTEB 屏蔽。

- 注 2: 当配置为 HS/XT/INTOSCH 16MHz 模式时,晶振稳定时间为 512XTosc; 当配置为 LP 模式时,晶振稳定时间大约为 1S 左右。

芯片下电复位使能和下电复位电压点可通过配置字 BORVS<1:0>位配置。

| BORVS<1:0> | 下电复位电压点配置     | 下电复位使能 |

|------------|---------------|--------|

| 11         | 低于 3.4V 时芯片复位 | 使能     |

| 10         | 低于 2.7V 时芯片复位 | 使能     |

| 01         | 低于 2.2V 时芯片复位 | 使能     |

| 00         |               | 禁止     |

表 5-3 下电复位电压点配置表

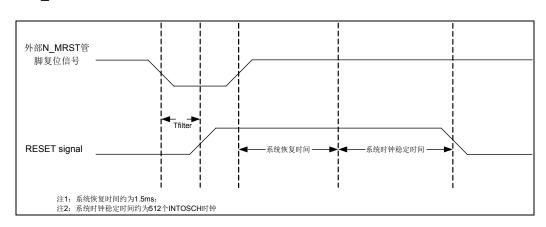

# 5.3.4 外部N MRST管脚复位

芯片提供外部 N\_MRST 管脚,当 CFG\_WD<5>(MRSTEN)为 1 时,用于系统复位。当复位管脚输入低电平信号时,系统复位。当复位管脚处于高电平时,系统正常运行。需要注意的是,在系统上电完成后,外部复位管脚必须输入高电平,否则系统将一直保持在复位状态。另外,需要特别注意的是,禁止将 N\_MRST 管脚直接连接到 VDD 上;禁止 N\_MRST 管脚上的电压高于 VDD 电压。

图 5-12 外部 N MRST 管脚复位

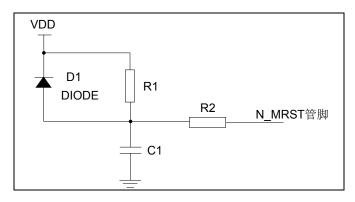

外部 N\_MRST 管脚复位电路有多种,以下介绍两种比较典型的连接电路。

#### 1. RC 复位

RC 复位电路是外部 N\_MRST 脚复位电路最简单的一种,对外界环境条件要求不高的情况下,可以采用此种连接方式。

图 5-13 N\_MRST 复位参考电路图 1

注: 采样 RC 复位,其中 47KΩ≤R1≤100KΩ,电容 C1 (0.1μF),R2 为限流电阻,0.1KΩ≤R2≤1KΩ。

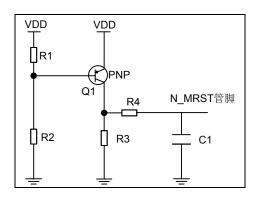

## 2. PNP 三极管复位

PNP三极管复位电路适用于对电源干扰较强的的场合。

图 5-14 N\_MRST 复位参考电路图 2

注: 采用 PNP 三极管复位,通过 R1(2K $\Omega$ )和 R2(10K $\Omega$ )分压作为基极输入,发射极接 VDD,集电极一路通过 R3(20K $\Omega$ )接地,另一路通过 R4(1K $\Omega$ )和 C1(0.1 $\mu$ F)接地,C1 另一端作为 N\_MRST 输入。

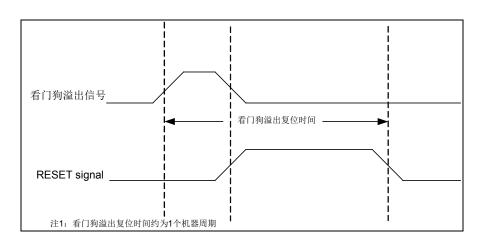

## 5.3.5 看门狗定时器溢出复位

看门狗复位是系统的一种保护设置。在正常状态下,由程序将看门狗定时器清零。若出错,系统处于未知状态,程序无法清除看门狗,导致看门狗定时器溢出,此时系统复位。看门 狗溢出复位后,系统重启进入正常状态。

图 5-15 看门狗溢出复位

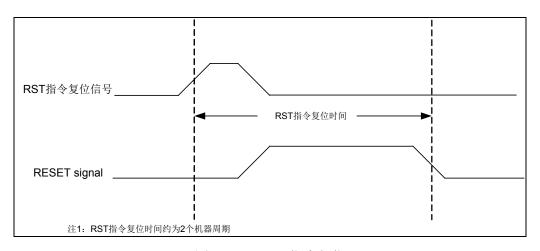

# 5.3.6 RST指令复位

整个芯片可通过执行 RST 指令复位,复位后,全部状态位都将被影响。

图 5-16 RST 指令复位

# 5.3.7 特殊功能寄存器

| PWRC | PWRC: 电源控制寄存器 |           |     |        |      |      |       |       |  |  |

|------|---------------|-----------|-----|--------|------|------|-------|-------|--|--|

| Bit  | 7             | 6         | 5   | 4      | 3    | 2    | 1     | 0     |  |  |

| Name | LPM           | VRST<1:0> |     | N_RSTI | N_TO | N_PD | N_POR | N_BOR |  |  |

| R/W  | R/W           | R/W       | R/W | R/W    | R    | R    | R/W   | R/W   |  |  |

| POR  | 0             | 1         | 0   | 1      | 1    | 1    | 0     | Х     |  |  |

"x": 未知

Bit 7 LPM: 休眠模式选择位

0: IDLE0 模式 1: IDLE1 模式

Bit 6~5 VRST<1:0>: LDO 稳定时间控制寄存器

当 CLKSS=1 时,

00: LDO 稳定时间为 16 个内部 32KHz 时钟周期 01: LDO 稳定时间为 32 个内部 32KHz 时钟周期 10: LDO 稳定时间为 64 个内部 32KHz 时钟周期

V1.4 49/95

11: LDO 稳定时间为 128 个内部 32KHz 时钟周期 当 CLKSS=0 时,

11: LDO 稳定时间为 128 个内部 32KHz 时钟周期 其它: LDO 稳定时间为 64 个内部 32KHz 时钟周期

Bit 4 N RSTI: 复位指令标志位

0: 执行复位指令(必须用软件置位)

1: 未执行复位指令

Bit 3 N\_TO: WDT 溢出标志位

0: WDT 计数溢出时被清零

1: 上电复位或执行 CWDT、IDLE 指令后被置 1

Bit 2 N PD: 低功耗标志位

0: 执行 IDLE 指令后清零

1: 上电复位或执行 CWDT 指令后置 1

Bit 1 N\_POR: 上电复位状态位

0: 上电复位发生(上电复位后,必须软件置位)

1: 无上电复位发生

Bit 0 N BOR: 低电压复位状态位

0: 低电压复位发生(低电压复位后,必须软件置位)

1: 无低电压复位发生

注:LDO 为芯片内置供电模块,给芯片内部电路模块供电。

# 5.4 低功耗操作

## 5. 4. 1 MCU低功耗模式

本芯片支持两种低功耗休眠模式: IDLE0 模式或 IDLE1 模式,通过设置 PWRC 寄存器位 LPM (PWRC<7>) 进行选择。

#### ◇ 支持 IDLE0 模式

- 当 LPM = 0 时, 执行 IDLE 指令, 芯片进入 IDLE0 模式:

- 时钟源停振(32KHz RC 时钟源除外),主系统时钟暂停

- 程序暂停、同步模块暂停、异步模块运行,器件功耗降低

- 支持低功耗唤醒,唤醒时间可配,同时需要考虑 LDO 稳定时间

- 所有 I/O 端口将保持进入 IDLEO 模式前的状态

- 若使能 WDT,则 WDT 将被清零并保持运行

- N PD 位被清零, N TO 位被置 1

#### ◇ 支持 IDLE1 模式

- 当 LPM = 1 时, 执行 IDLE 指令, 芯片进入 IDLE1 模式:

- 时钟源保持运行, 主系统时钟暂停

- 程序暂停、同步模块暂停、异步模块运行,器件功耗降低

- 支持低功耗唤醒,唤醒时间可配,最小1个机器周期

- 所有 I/O 端口将保持进入 IDLE1 前的状态

- 若使能 WDT,则 WDT 将被清零并保持运行

- N\_PD 位被清零, N\_TO 位被置 1

## 5.4.2 低功耗模式配置

两种低功耗模式 IDLE0 和 IDLE1 模式的选择由 PWRC 寄存器中的 LPM 位控制。当 LPM = 0 时,执行 IDLE 指令,芯片进入 IDLE0 模式;当 LPM = 1 时,执行 IDLE 指令,芯片进入 IDLE1 模式。

| 低功耗模式    | LPM |

|----------|-----|

| IDLE0 模式 | 0   |

| IDLE1 模式 | 1   |

表 5-4 低功耗模式配置表

为了降低功耗,所有 I/O 管脚都应保持为 VDD 或 VSS。为了避免输入管脚悬空而引入开关电流,应在外部将高阻输入的 I/O 管脚拉为高电平或低电平,N\_MRST 管脚必须处于逻辑高电平。

# 5. 4. 3 IDLE唤醒方式配置

当系统进入低功耗模式后,程序处于暂停状态,以下几种方式可将系统唤醒。

| 序号 | 唤醒源    | 中断屏蔽  | 中断使能 | 中断模式  | 备注     |

|----|--------|-------|------|-------|--------|

| 1  | N_MRST | -     | -    | -     | 外部复位   |

| 2  | WDT    | -     | -    | -     | WDT 溢出 |

| 3  | KINT0  | KMSK0 | KIE  | 默认/向量 | 外部按键中断 |

V1.4 51/95

| 序号 | 唤醒源   | 中断屏蔽  | 中断使能   | 中断模式  | 备注      |

|----|-------|-------|--------|-------|---------|

|    | KINT1 | KMSK1 |        |       |         |

|    | KINT2 | KMSK2 |        |       |         |

|    | KINT3 | KMSK3 |        |       |         |

|    | KINT4 | KMSK4 |        |       |         |

| 4  | PINT  | -     | PIE    | 默认/向量 | 外部端口中断  |

| 5  | LVDn  | -     | LVDnIE | 默认/向量 | LVDn 中断 |

表 5-5 休眠唤醒表

- 注 1: 低功耗唤醒与全局中断使能无关,只需相应中断源使能位置位为"1"即可。在低功耗模式时,若外设产生中断信号,即使全局中断使能 GIE 为 0,低功耗模式依然会被唤醒,只是唤醒后不会执行中断程序。

- 注 2: 关于外部按键中断使用,当开启中断使能和中断屏蔽位使能前,先对端口寄存器进行读或者写的操作,然后 清除中断标志位,以免误产生中断。

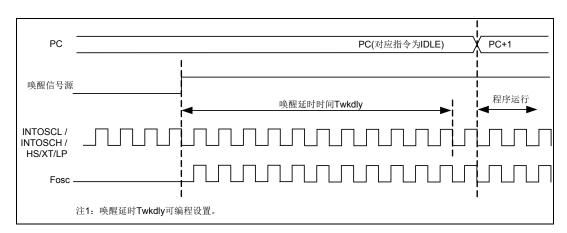

# 5.4.4 唤醒时序图

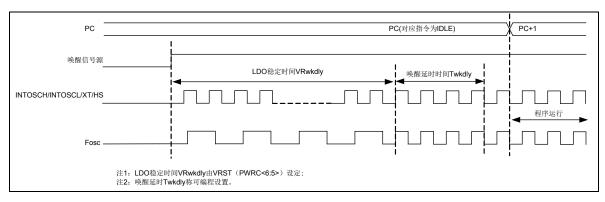

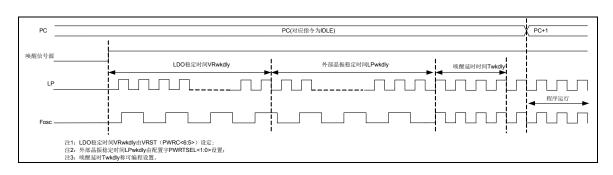

当唤醒事件发生后,芯片根据配置字 OSCS<2:0>的配置执行下述操作:

- ◇ 当 OSCS<2:0>配置为 HS/XT/INTOSCO/INTOSC 模式时:

- 在 IDLE0 模式(LPM=0)下,芯片需要先等待 VRwkdly 时间(由 VRST(PWRC<6:5>) 设定),此时间称为 LDO 稳定时间,之后芯片主时钟运行一段 Twkdly 时间后才执行 IDLE 下一条指令,Twkdly 称为唤醒延时,唤醒延时可通过 WKDC 寄存器设置;

- 在 IDLE1 模式(LPM=1)下,芯片仅等待 Twkdly 时间后就执行 IDLE 下一条指令, 无 VRwkdly 时间。

- ◇ 当 OSCS<2:0>配置为 LP 模式时:

- 在 IDLE0 模式(LPM=0)下,芯片需要先等待 VRwkdly 时间(由 VRST(PWRC<6:5>) 设定),此时间称为 LDO 稳定时间,接着芯片等待 LPwkdly 时间,之后芯片主时钟运行一段 Twkdly 时间后才执行 IDLE 下一条指令,Twkdly 称为唤醒延时,唤醒延时可通过 WKDC 寄存器设置;

- 在 IDLE1 模式(LPM=1)下,芯片仅等待 Twkdly 时间后就执行 IDLE 下一条指令, 无 VRwkdly 和 LPwkdly 时间。

| OSCS 配置 | 低功耗模式     | 计算公式                                              |

|---------|-----------|---------------------------------------------------|

| 所有模式    | IDLE1 模式  | (WKDC[7:0]+1) × 2 Tosc                            |

| 非 LP 模式 | IDI E0 档子 | VRwkdly + (WKDC[7:4] + 1) × 16 × 2 Tosc           |

| LP 模式   | IDLE0 模式  | VRwkdly + LPwkdly + (WKDC[7:4] + 1) × 16 × 2 Tosc |

表 5-6 休眠唤醒时间表

图 5-17 HS/XT/INTOSCO/INTOSC 模式时,系统唤醒 IDLE0 时序图

图 5-18 LP 模式时,系统唤醒 IDLE0 时序图

图 5-19 HS/XT/INTOSCO/INTOSC/LP 模式时,系统唤醒 IDLE1 时序图

# 5.4.5 特殊功能寄存器

| WKDC: 唤醒延时控制寄存器 |           |     |     |     |     |     |     |     |

|-----------------|-----------|-----|-----|-----|-----|-----|-----|-----|

| Bit             | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Name            | WKDC<7:0> |     |     |     |     |     |     |     |

| R/W             | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR             | 1         | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

Bit 7~0 WKDC<7:0>: 唤醒延时时间设置位

00<sub>H</sub>: 延时最短

. . . . . .

FF<sub>H</sub>: 延时最长

# 第6章 外设

# 6.1 定时器/计数器模块(Timer/Counter)

本芯片包含 1 组 8 位定时器/计数器 (T8N)、2 组 PWM 时基定时器 (T8P1/T8P2)。

# 6.1.1 8 位定时器/计数器(T8N)

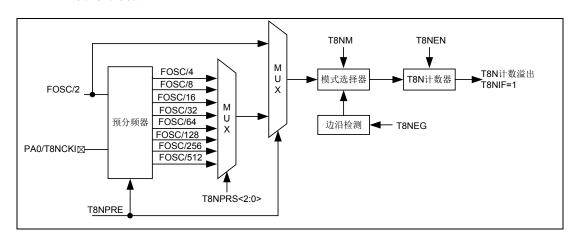

#### 6.1.1.1 概述

8 位定时器/计数器包括定时器和计数器两种工作模式。定时器模式根据寄存器制定的定时时间进行定时,可以使定时器有选择地产生中断请求或完成其它操作。计数器模式用于对外部时钟信号(T8NCKI)进行计数。

- ◇ T8N 支持两种工作模式

- 定时器模式(时钟源为系统时钟二分频(Fosc/2)

- 同步计数器模式(时钟源为外部输入时钟 T8NCKI)

- ◇ T8N 支持以下功能组件

- 8 位预分频器 (无实际物理地址,不可读写)

- 8 位计数器(T8N)

- 8 位控制寄存器 (T8NC)

- ◇ 中断和暂停

- 支持溢出中断标志(T8NIF)

- 支持中断处理

- ◇ 在 IDLE 模式下, T8N 暂停工作

# 6.1.1.2 内部结构图

图 6-1 T8N 内部结构图

#### 6.1.1.3 工作模式

8 位定时器/计数器共有两个模式: 定时器模式和同步计数器模式,两种不同模式的时钟源分别来自 Fosc/2 和外部 T8NCK 管引脚输入时钟。

| T8NM | 工作模式    | 时钟源    |

|------|---------|--------|

| 0    | 定时器模式   | Fosc/2 |

| 1    | 同步计数器模式 | T8NCKI |

表 6-1 T8N 工作模式配置表

## 6.1.1.4 预分频器

预分频器可以提供定时器/计数器一个更长的溢出周期。当 T8NC 寄存器中的 T8NPRE 为"1"时,使能 T8N 预分频器。任何对 T8N 计数器的写操作都会清零预分频器,但不影响预分频器的分频比设置,预分频器的计数值无法读写。预分频器的分频比可通过 T8NC 寄存器中的 T8NPRS <2:0>位进行设置,预分频比范围为 1:2~1:256。

| 工作模式  | T8NPRE | T8NPRS<2:0> | T8N 计数时钟   |

|-------|--------|-------------|------------|

|       | 0      | -           | Fosc/2     |

|       | 1      | 000         | Fosc/4     |

|       | 1      | 001         | Fosc/8     |

|       | 1      | 010         | Fosc/16    |

| 定时器模式 | 1      | 011         | Fosc/32    |

|       | 1      | 100         | Fosc/64    |

|       | 1      | 101         | Fosc/128   |

|       | 1      | 110         | Fosc/256   |

|       | 1      | 111         | Fosc/512   |

|       | 0      | -           | T8NCKI     |

|       | 1      | 000         | T8NCKI/2   |

|       | 1      | 001         | T8NCKI/4   |

|       | 1      | 010         | T8NCKI/8   |

| 计数器模式 | 1      | 011         | T8NCKI/16  |

|       | 1      | 100         | T8NCKI/32  |

|       | 1      | 101         | T8NCKI/64  |

|       | 1      | 110         | T8NCKI/128 |

|       | 1      | 111         | T8NCKI/256 |

表 6-2 T8N 预分频器配置表

#### 6.1.1.5 工作模式

T8N 有定时器和计数器两种工作模式,定时器模式和计数器模式,通过 T8NM 进行选择。定时器和计数器计数模式均支持预分频器。配置为定时器模式时,T8N 计数器的时钟源为系统时钟 2 分频 (Fosc/2);配置为计数器模式时,T8N 计数器的时钟源为经系统机器周期同步的外部输入时钟 T8NCKI。因此,T8NCKI输入的高电平和低电平时间都至少为一个机器周期。通过 T8NC 寄存器中的 T8NEG 位选择外部时钟的计数边沿为上升沿或下降沿。

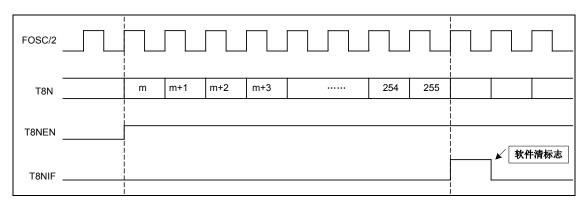

## 6.1.1.6 定时器模式

T8N 计数器为递增计数,计数值由 FF<sub>H</sub>变为 00<sub>H</sub>时,T8N 计数器发生溢出并重新开始计数。T8N 计数器发生溢出,中断标志 T8NIF 位被置"1"。如果中断使能位 T8NIE 和全局

中断使能位 GIE 都为"1",则向 CPU 发出 T8N 溢出中断响应请求。为了避免误触发中断,在重新使能这个中断之前,T8NIF 位必须软件清零。在 CPU 进入休眠模式后,T8N 模块不工作,因此不产生中断。

当 T8N 配置为定时器模式时,若禁止预分频器,T8N 计数器的时钟为系统时钟二分频 (Fosc/2);若使能预分频器,分频器对 Fosc/2 或者 WDT\_RC 时钟进行分频,此时,T8N 计数器的计数时钟为分频后的时钟。

图 6-2 定时器模式时序图

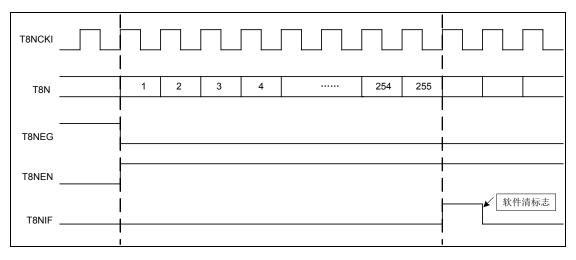

#### 6.1.1.7 同步计数器模式

当 T8N 配置为同步计数器模式时,若禁止预分频器,T8N 计数器的时钟为外部输入时钟 T8NCKI, 内部相位时钟 p2 将对时钟 T8NCKI 进行同步。所以 T8NCKI 保持高电平或者 低电平的时间至少为一个机器周期。通过设置 T8NEG (T8NC<4>)选择外部时钟的计数 边沿为上升沿或下降沿。

同样,计数器模式也支持预分频器对外部时钟 T8NCKI 进行分频。并且,T8NCKI 复用的 IO 端口必须配置为数字输入状态。

当 T8N 计数器递增计数由 FFH 变为 00H 时,T8N 计数器发生溢出,中断标志 T8NIF 位被置"1"。如果中断使能位 T8NIE 和全局中断使能位 GIE 都为"1",则向 CPU 发出 T8N溢出中断响应请求。为了避免误触发中断,在重新使能这个中断之前,T8NIF 位必须软件清零。在 CPU 进入休眠模式后,T8N 模块不工作,因此不产生中断。

图 6-3 计数器模式时序图 (T8NEG=0, T8NCKI上升沿计数)

## 6.1.1.8 特殊功能寄存器

8 位定时器/计数器 T8N 由两个寄存器控制,一个 8 位计数器 T8N 和一个控制寄存器 T8NC。T8N 寄存器用于存放计数值,T8NC 控制寄存器用于控制 T8N 的使能、T8N 的模式选择、T8NCKI 计数边沿选择、预分频器使能位以及预分频器分频比选择。

| T8N: T8 | T8N: T8N 计数器 |     |     |     |     |     |     |     |

|---------|--------------|-----|-----|-----|-----|-----|-----|-----|

| Bit     | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Name    | T8N<7:0>     |     |     |     |     |     |     |     |

| R/W     | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| POR     | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

Bit 7~0 T8N<7:0>: 8 位 T8N 计数值

| T8NC: 1 | T8NC: T8N 控制寄存器 |   |      |       |        |     |           |     |

|---------|-----------------|---|------|-------|--------|-----|-----------|-----|

| Bit     | 7               | 6 | 5    | 4     | 3      | 2   | 1         | 0   |

| Name    | T8NEN           | _ | T8NM | T8NEG | T8NPRE | T   | 8NPRS<2:0 | )>  |

| R/W     | R/W             | _ | R/W  | R/W   | R/W    | R/W | R/W       | R/W |

| POR     | 0               | 0 | 0    | 0     | 0      | 0   | 0         | 0   |

Bit 7 T8NEN:T8N 使能位

0: 关闭

1: 使能

Bit 6 未使用

Bit 5 T8NM: T8N 模式选择位

0: 定时器模式(时钟源为系统时钟二分频 Fosc/2)

1: 同步计数器模式(时钟源为 T8NCKI)

Bit 4 T8NEG: T8NCKI 计数边沿选择位

0: T8NCKI 上升沿计数

1: T8NCKI 下降沿计数

Bit 3 T8NPRE: 预分频器使能位

0: 禁止

1: 使能

Bit 2~0 T8NPRS <2:0>: 预分频器分频比选择位

000: 1:2

001: 1:4

010: 1:8

011: 1:16

100: 1:32

101: 1:64

110: 1:128

111: 1:256

#### 6.1.2 两路 8 位PWM时基定时器(T8P1/T8P2)

#### 6.1.2.1 概述

8 位 PWM 时基定时器 T8P1/T8P2 支持两种工作模式,定时器模式和 PWM 模式。定时器模式根据寄存器制定的定时时间进行定时,可以使定时器有选择地产生中断请求或完成其它操作。PWM 模式用于 PWM 输出。

- ◇ T8Pn 支持两种工作模式(时钟源为系统时钟 2 分频(Fosc/2))

- 定时器模式

- PWM 模式,最高 9 位精度

- ◇ T8Pn 支持以下功能组件

- -4位的预分频器和后分频器(无实际物理地址,软件不可读写)

- 8 位计数器 (T8Pn)

- 8 位精度寄存器(T8PnRL)

- 8 位精度缓冲寄存器(T8PnRH)(在 PWM 模式下,软件不可写)

- 8 位周期寄存器(T8PnP)

- 8 位周期缓冲器 (PRDBUF, 无实际物理地址, 软件不可读写)

- T8Pn 控制寄存器(T8P1C/T8P2C)

- PWM 精度控制寄存器 (PWMnC)

- T8Pn 输出控制寄存器(T8PnOC)

- ◇ 中断和暂停

- 支持匹配中断标志(T8PnIF)和周期中断(T8PnPIF)

- 支持中断处理

- 在 IDLE 模式下, T8Pn 暂停工作

## 6.1.2.2 内部结构图

图 6-4 T8P1/T8P2 内部结构图

#### 6.1.2.3 工作模式

8 位 PWM 时基定时器共有两个模式: 定时器模式和 PWM 模式,通过 T8PnC 寄存器中的 T8PnM 位进行设置选择。

V1.4 58/95

| T8PnM | 工作模式   |

|-------|--------|

| 0     | 定时器模式  |

| 1     | PWM 模式 |

表 6-3 T8Pn 工作模式配置表

## 6.1.2.4 预分频器和后分频器

预分频器和后分频器可以提供一个更长的溢出和中断周期。T8Pn 模块计数器支持可配置的 4 位预分频器和可配置的 4 位后分频器。预分频器与后分频器的计数值都无法读写,修改 T8Pn 的控制寄存器或计数器都会把预分频器和后分频器清零,但不改变分频比设置。预分频器的分频比可通过 T8PnC 寄存器中的 T8PnPRS <1:0>位进行设置,预分频比范围为 1:1~1:16。后分频器的分频比可通过 T8PnC 寄存器中的 T8PnPOS <3:0>位进行设置,后分频比范围为 1:1~1:16。

需要注意的是,预分频器分频比和后分频器分频比设置不能同时大于 1:1,即当预分频器分频比为 1:1 时,才可设置后分频器分频比,同理,当设置预分频器分频比前,需先确保后分频器分频比为 1:1。

| T8PnPOS<3:0> | T8PnPRS<1:0> | T8Pn 定时器时钟频率 |

|--------------|--------------|--------------|

| 0000         | 00           | Fosc/2       |

| 0000         | 01           | Fosc/8       |

| 0000         | 1x           | Fosc/32      |

| 其它值          | _            | _            |

表 6-4 T8P1/T8P2 预分频器配置表

| T8PnPRS<1:0> | T8PnPOS<3:0> | T8Pn 匹配中断        |

|--------------|--------------|------------------|

| 00           | 0000         | 计数器与周期寄存器匹配 1 次  |

| 00           | 0001         | 计数器与周期寄存器匹配 2 次  |

| 00           | 0010         | 计数器与周期寄存器匹配3次    |

| 00           | 0011         | 计数器与周期寄存器匹配 4次   |

| 00           | 0100         | 计数器与周期寄存器匹配 5 次  |

| 00           | 0101         | 计数器与周期寄存器匹配 6次   |

| 00           | 0110         | 计数器与周期寄存器匹配7次    |

| 00           | 0111         | 计数器与周期寄存器匹配8次    |

| 00           | 1000         | 计数器与周期寄存器匹配9次    |

| 00           | 1001         | 计数器与周期寄存器匹配 10 次 |

| 00           | 1010         | 计数器与周期寄存器匹配 11 次 |

| 00           | 1011         | 计数器与周期寄存器匹配 12 次 |

| 00           | 1100         | 计数器与周期寄存器匹配 13次  |

| 00           | 1101         | 计数器与周期寄存器匹配 14 次 |

| 00           | 1110         | 计数器与周期寄存器匹配 15 次 |

| 00           | 1111         | 计数器与周期寄存器匹配 16 次 |

| 其它值          | _            | _                |

表 6-5 T8P1/T8P2 后分频器配置表

#### 6. 1. 2. 5 工作模式

T8P1/T8P2 有两种工作模式,定时器模式和 PWM 模式,通过 T8PnM 进行模式选择。两种模式均支持预分频器和后分频器。两种模式下,T8Pn 计数器的时钟源均为系统时钟 2 分频 (Fosc/2)。

#### 6.1.2.6 定时器模式

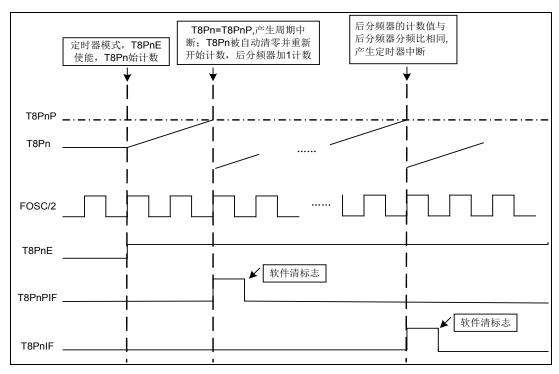

当 T8PnM=0 且 T8PnE=1 时, T8Pn 工作在定时器模式。

在定时器模式下,T8Pn 计数器的时钟源为系统时钟二分频 Fosc/2,可选择预分频器对计数时钟进行分频,计数器的计数时钟为分频后的时钟。

T8Pn 在定时器模式下对计数时钟进行递增计数,当 T8Pn 的计数值与周期寄存器 T8PnP(当 T8PnPM=0)或与周期缓冲器 PRDBUF(当 T8PnPM=1)相等时,将周期中断 T8PnPIF 置 1,该中断标志需要软件清零。同时 T8Pn 被自动清零并重新开始计数,后分频器加 1 计数。当后分频器的计数值与后分频器分频比相同时,复位后分频器,并将中断标志 T8PnIF 置 1,该中断标志需要软件清零。

T8PnP 寄存器的缓冲寄存器为周期缓冲器 PRDBUF, 当 T8Pn 的计数值与 PRDBUF 相等且 T8PnPM=1 时,将 T8PnP 寄存器的内容更新至周期缓冲器 PRDBUF。

注:在设置 T8PnM=0 且 T8PnPM=1 后,再使能 T8PnE=1,确保在定时器模式起始时,能将周期寄存器 T8PnP的值更新至周期缓冲器 PRDBUF。

图 6-5 T8Pn 定时器模式时序图

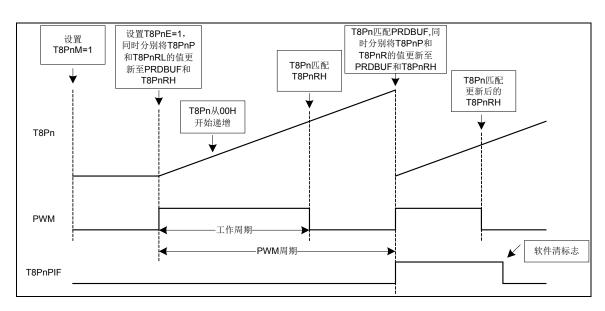

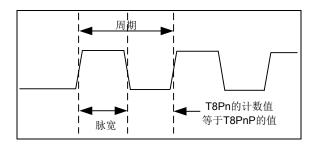

#### 6.1.2.7 PWM输出模式

当 T8PnM=1 且 T8PnE=1 时, T8Pn 工作在 PWM 输出模式。计数时钟源为系统时钟二 分频 Fosc/2, 并支持预分频器。后分频器的设置不影响 PWM 输出周期和占空比, 只影

V1.4 60/95

响匹配中断 T8PnIF 中断标志位的产生,详见《T8Pn 后分频器配置表》。

如下图所示,在 PWM 模式(T8PnM=1)下,当 T8PnE=0 时,PWM 输出关闭,并保持 PWM 输出为 0;设置 T8PnE 为 1 时,PWM 输出波形启动,PWM 输出起始为 1,同时 分别将 T8PnP 和 T8PnRL 寄存器的内容更新至缓冲器 PRDBUF 和精度缓冲寄存器 T8PnRH(缓冲器软件不可读写),随后 T8Pn 从零开始递增计数,当 T8Pn 与 T8PnRH 的值相等时,PWM 输出改变为 0,并继续递增计数。当 T8Pn 的计数值与 PRDBUF 相等时,PWM 输出恢复为 1,同时 PRDBUF 和 T8PnRH 再次分别载入 T8PnP 和 T8PnRL 寄存器的值,并产生周期中断 T8PnPIF 中断标志,该中断标志需要软件清零。同时 T8Pn被自动清零并重新开始计数,后分频器加 1 计数。至此一个完整的 PWM 周期完成,随后继续循环新的 PWM 周期。当后分频器的计数值与后分频器分频比相同时,复位后分频器,并将中断标志 T8PnIF 置 1,该中断标志需要软件清零。

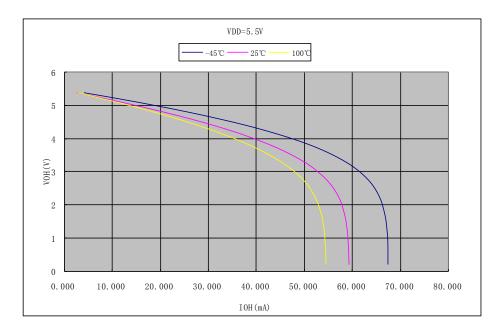

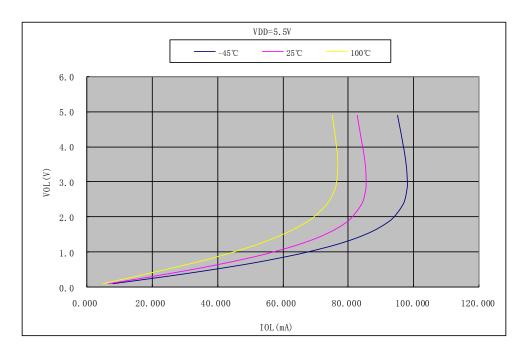

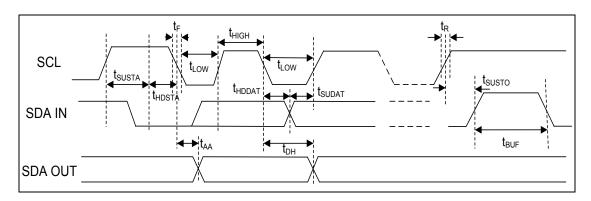

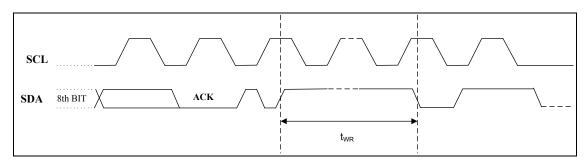

通过设置 T8P1EN<1:0> (T8P1OC<1:0>) 和 T8P2EN<1:0> (T8P2OC<1:0>), 并且 PWM 复用 IO 的 PxT 设置为输出状态时,则相应的 Px 端口输出 PWM 波形。